(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

## SUMMER- 18 EXAMINATION

Subject Name: Basic Electronics <u>Model Answer</u> Subject Code:

22216

#### **Important Instructions to examiners:**

- 1) The answers should be examined by key words and not as word-to-word as given in the model answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may try to assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given more Importance (Not applicable for subject English and Communication Skills.

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figures drawn by candidate and model answer may vary. The examiner may give credit for any equivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constant values may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent concept.

| Q.<br>No. | Sub<br>Q. N. |                      | Answers                                           |                             |                       |  |

|-----------|--------------|----------------------|---------------------------------------------------|-----------------------------|-----------------------|--|

| 1         |              | Attempt any FIVE:    |                                                   |                             | 10-<br>Total<br>Marks |  |

|           | а            | State materials used | d for LED's to emit different o                   | olour light.                | 2M                    |  |

|           | Ans:         |                      |                                                   |                             | ½ Mark                |  |

|           |              | Sr. No.              | Material used                                     | Colour of the emitted light | for each              |  |

|           |              | 1                    | Gallium arsenide (GaAs)                           | Infrared (IR)               | correct answer        |  |

|           |              | 2                    | Gallium arsenide phospide                         | Red or Yellow               | -                     |  |

|           |              |                      | GaAsP                                             |                             |                       |  |

|           |              | 3                    | Gallium phospide (GaP)                            | Red or Green                | -                     |  |

|           |              | 4                    | Gallium nitrite Ga(NO <sub>2</sub> ) <sub>3</sub> | Blue                        |                       |  |

|           | b            | Sketch the symbol o  | of P-channel and n-channel d                      | epletion type MOSFET.       | 2M                    |  |

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

# **SUMMER-18 EXAMINATION**

**Subject Name: Basic Electronics Model Answer**

| Ans: |                                                                      | 1M<br>each     |  |  |  |

|------|----------------------------------------------------------------------|----------------|--|--|--|

|      | Gate  Gate  Gate  Source  Source  p channel                          |                |  |  |  |

| С    | List any two BJT biasing circuits with respect to operating point.   | 2M             |  |  |  |

| Ans: | 1) Fixed bias                                                        | Any            |  |  |  |

|      | 2) Base biased with emitter feedback                                 | two 1N<br>each |  |  |  |

|      | 3) Collector to base bias                                            |                |  |  |  |

|      | 4) Voltage divider bias                                              |                |  |  |  |

| d    | State different methods of biasing of FET.                           | 2M             |  |  |  |

| Ans: | 1) Fixed bias                                                        | ½ M<br>each    |  |  |  |

|      | 2) Self bias                                                         |                |  |  |  |

|      | 3) Voltage divider bias                                              |                |  |  |  |

|      | 4) Source bias                                                       |                |  |  |  |

| е    | Sketch reverse characteristics of zener diode with proper labelling. | 2M             |  |  |  |

| Ans: | $V_z$ $V_R$ (Volts) 0                                                | 1M             |  |  |  |

|      | K I <sub>zk</sub>                                                    | diagra<br>m    |  |  |  |

|      | Breakdown (or regulation region)                                     | 1M             |  |  |  |

|      | (or regulation region)                                               | labelin        |  |  |  |

|      | M I <sub>ZM</sub>                                                    |                |  |  |  |

|      | Reverse characteristic of a zener diode.                             |                |  |  |  |

| f    | Define line regulation. State the formula for its regulation.        | 2M             |  |  |  |

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

## SUMMER- 18 EXAMINATION

Subject Name: Basic Electronics Model Answer Subject Code: 22216

|   | Ans: | Line regulation:-It is the ability of the power supply to maintain its specified output voltage                        |            |

|---|------|------------------------------------------------------------------------------------------------------------------------|------------|

|   |      | over changes in the input line voltage. It is expressed as percent of change in the output                             |            |

|   |      | voltage relative to the change in the input line voltage.                                                              |            |

|   |      | Formula:-                                                                                                              |            |

|   |      | $Line\ regulation = \left(\frac{\Delta V_{OUT}}{\Delta V_{IN}}\right) \!\!\times\! 100\%$ $\Delta$ means "a change in" |            |

|   |      |                                                                                                                        |            |

|   |      | (OR)                                                                                                                   |            |

|   |      | The change in output voltage with respect to per unit change in input voltage is defined as                            |            |

|   |      | line regulation. It is mathematically expressed as,                                                                    |            |

|   |      | Line regulation= $\Delta V_L/\Delta V_S$                                                                               |            |

|   |      | Where,                                                                                                                 |            |

|   |      | $\Delta V_L$ = The change in output voltage                                                                            |            |

|   |      | $\Delta V_S$ = The change in input voltage                                                                             |            |

|   | g    | State cut in voltage value of diode for silicon and germanium.                                                         | 2M         |

|   | Ans: | The cut in voltage value of diode for silicon is 0.7 Volt and for Germanium is 0.3 Volt                                | 1M<br>each |

| 1 | 1    |                                                                                                                        | I          |

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

# **SUMMER-18 EXAMINATION**

**Subject Name: Basic Electronics Model Answer**

| Q.<br>No. | Sub<br>Q. N. | Answers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Marking<br>Scheme  |

|-----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 2         |              | Attempt any THREE:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12- Total<br>Marks |

|           | а            | Describe experimental set-up for operation of P-N junction diode in forward bias. Draw its characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4M                 |

|           | Ans:         | Experimental set up Forward characteristics:-  Rs  VFF  P  VAK  Explanation:-  PN junction diode is forward biased when positive terminal of the power supply is connected to the P-type side, and the negative terminal of the power supply is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2M                 |

|           |              | <ul> <li>When a PN junction is forward biased, the holes are repelled from the positive terminal of the battery and are moved towards the junction.</li> <li>Similarly the free electrons are repelled from the negative terminal of the battery and move towards the PN junction.</li> <li>Because of their acquired energy (from the battery V<sub>FF</sub>), some of the holes and the free electrons enter into the depletion region and recombine themselves.</li> <li>This reduces the potential barrier and the width of the depleting region.</li> <li>The width of depletion region and the barrier potential reduces with the increase in forward bias.</li> <li>As a result of this, more majority carriers diffuse across the junction. Therefore, it</li> </ul> |                    |

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

# **SUMMER-18 EXAMINATION**

**Subject Name: Basic Electronics Model Answer**

|      | causes a large current to flow through the PN junction. This is called forward current.  • The point at which this sudden increase in current takes place is represented as the "knee" point  • The PN junction does not permit the current to flow until the external bias voltage overcomes the barrier potential V <sub>B</sub> . The external bias voltage should be greater than the barrier potential for the current to flow.  Forward characteristics:    I <sub>F</sub> in mA | 1M     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| b    | Define alpha and beta of a transistor and state the relation between them.                                                                                                                                                                                                                                                                                                                                                                                                             | 4M     |

| Ans: | Definition: Alpha( $\alpha$ ) is the current gain of CB configuration. It is defined as the ratio of collector current( $I_C$ ) to emitter current ( $I_E$ ). Beta( $\beta$ ) is the current gain of CE configuration. It is defined as the ratio of collector current( $I_C$ ) to base current ( $I_B$ ). Relation between $\alpha$ & $\beta$ :                                                                                                                                       | 1M eac |

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

### SUMMER- 18 EXAMINATION

**Subject Name: Basic Electronics Model Answer**

Subject Code: 22216

Current gain ( $\alpha$ ) of CB configuration =  $\frac{I_C}{I_E}$ Current gain of ( $\beta$ ) of CE configuration =  $\frac{I_C}{I_B}$

We know that;

$$I_E = I_B + I_C$$

....(1)

(OR)

Dividing equation (1) by I<sub>C</sub>

$$\frac{I_E}{I_C} = \frac{I_B}{I_C} + \frac{I_C}{I_C}$$

Therefore  $\frac{1}{\alpha} = \frac{1}{8} + 1$

[since  $\alpha = \frac{l_C}{l_E}$ ,  $\beta = \frac{l_C}{l_B}$ ]

Therefore  $\frac{1}{\alpha} = \frac{1+\beta}{\beta}$

$$\alpha (1 + \beta) = \beta$$

$$\alpha + \alpha \beta = \beta$$

$$\alpha = \beta - \alpha \beta$$

$$\alpha = \beta(1 - \alpha)$$

Therefore  $\beta = \frac{\alpha}{1-\alpha}$   $\alpha = \frac{\beta}{1+\beta}$

2M

Relation Between Current Grain & and Current Grain of CB congry (d) = AIC -1 Current Grain of CE config. (B) = AIC - 2 We know that emitter current (IE) of a transister is the sum of it's base current (IB) and collector current (IC) i.p. IE = IC + IB DIE = DIC+DIB DIB = DIE - DIC DIE = DIC + DIB

Pur value of DIB

in equi D

in equi D

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

# **SUMMER-18 EXAMINATION**

**Subject Name: Basic Electronics Model Answer**

| С    | Explain basic block diagram of regulated DC power supply, draw its input and output waveforms.                                        | 4M    |

|------|---------------------------------------------------------------------------------------------------------------------------------------|-------|

| Ans: | Block diagram of regulated DC power supply:-                                                                                          | 2M    |

|      | Explanation                                                                                                                           |       |

|      | 1)Transformer                                                                                                                         |       |

|      | 2) Rectifier                                                                                                                          |       |

|      | 3) Filter                                                                                                                             |       |

|      | 4) Voltage regulator.                                                                                                                 |       |

|      | 1. Transformer:- The AC main voltage is applied to a step down transformer. It reduces                                                |       |

|      | the amplitude of ac voltage to the desired level and applies it to a rectifier.                                                       |       |

|      | 2. Rectifier: The rectifier is usually a centre tapped or bridge type full wave rectifier. It                                         | 2M fo |

|      | converts the ac voltage into a pulsating dc voltage.                                                                                  | ion   |

|      | 3. Filter: The pulsating dc (or rectified ac) voltage contains large ripple. This voltage is                                          |       |

|      | applied to the filter circuit and it removes the ripple. The function of a filter is to                                               |       |

|      | remove the ripples to provide pure DC voltage at its output.                                                                          |       |

|      | The DC output voltage thus obtained will change with the changes in load current,input voltage, etc. So it is unregulated DC voltage. |       |

|      | 4. Voltage Regulator: The unregulated DC voltage is applied to a voltage regulator. Output                                            |       |

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

#### **SUMMER-18 EXAMINATION Subject Name: Basic Electronics Model Answer**

| d    | Explain the need of stabilization of Q point.                                             | 4N  |

|------|-------------------------------------------------------------------------------------------|-----|

| Ans: | Bias stabilization is a process of stabilizing the position of operating point "Q"        | 4IV |

|      | The stabilization of Q-point is necessary to maintain the Q-point at the centre of load   |     |

|      | line because the bias point (Q-point) changes its position on the load line due to the    |     |

|      | factors such as temperature or device to device variations.                               |     |

|      | If the Q-point gets shifted towards saturation or cut off regions, then amplified output  |     |

|      | waveform is distorted. In order to avoid such distortion it is necessary to stabilize the |     |

|      | Q-point at the centre of the load line.                                                   |     |

|      | So we need to design a biasing circuit which will keep the position of Q-point stable on  |     |

|      | the load line.                                                                            |     |

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

## **SUMMER-18 EXAMINATION**

**Subject Name: Basic Electronics Model Answer**

| Q.<br>No. | Sub<br>Q.<br>N. | Answers                                                                                                                                           | Marking<br>Scheme    |

|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 3         |                 | Attempt any four:                                                                                                                                 | 16- Total<br>Marks   |

|           | а               | Describe circuit diagram of bridge rectifier, draw its input and output waveforms.                                                                | 4M                   |

|           | Ans:            | Circuit diagram:                                                                                                                                  | Circuit<br>diagram2M |

|           |                 | A.C. Supply                                                                                                                                       | Explanation 1M       |

|           |                 | D <sub>2</sub> D <sub>3</sub> R V <sub>Out</sub>                                                                                                  | Waveform<br>1M       |

|           |                 | When input AC signal is applied across the bridge rectifier, during the positive half cycle                                                       |                      |

|           |                 | diodes D <sub>1</sub> and D <sub>2</sub> are forward biased and conduct while the diodes D <sub>3</sub> and D <sub>4</sub> are reverse            |                      |

|           |                 | biased and current flows through the load from point A-D <sub>1</sub> -load-D <sub>2</sub> -point B.                                              |                      |

|           |                 | During the negative half cycle diodes D <sub>3</sub> and D <sub>4</sub> are forward biased and conduct while                                      |                      |

|           |                 | diodes $D_1$ and $D_2$ are reverse biased and current flow through the load from point B-D <sub>3</sub> -load-D <sub>4</sub> -point A.            |                      |

|           |                 | As the current flowing through the load is unidirectional, the voltage developed across the load is also unidirectional as shown in the waveform. |                      |

|           |                 | Vout Vout D1D2 D3D4 D1D2 D3D4  t                                                                                                                  |                      |

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

## **SUMMER-18 EXAMINATION**

**Subject Name: Basic Electronics Model Answer**

| b    | Explain the working of positive clamper with proper circuit diagram and draw the                                                                                                | 4M                 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

|      | waveforms at input & output of clamper.                                                                                                                                         |                    |

| Ans: | Positive clamper circuit:                                                                                                                                                       | Circuit<br>diagram |

|      | V <sub>m</sub>                                                                                                                                                                  | Explanat<br>1M     |

|      |                                                                                                                                                                                 | Wavefor<br>1M      |

|      | Fig. 2 Positive Clamper                                                                                                                                                         |                    |

|      | <ul> <li>The circuit will be called a positive clamper, when the signal is pushed upward by<br/>the circuit.</li> </ul>                                                         |                    |

|      | During the positive half cycle, the diode is reverse biased.                                                                                                                    |                    |

|      | <ul> <li>During the negative half cycle, it is forward biased and current flows through it. It<br/>charges the capacitor to the negative peak voltage -V<sub>m</sub></li> </ul> |                    |

|      | <ul> <li>Once the capacitor is fully charged to -V<sub>m</sub>, cannot discharge because the diode<br/>cannot conduct in the reverse direction.</li> </ul>                      |                    |

|      | Therefore the capacitor acts as a battery with e.m.f equal to -V <sub>m</sub> .                                                                                                 |                    |

|      | $ullet$ This voltage gets added to the input signal, $V_m$ . $sin \omega t$ .                                                                                                   |                    |

|      | $ullet$ Therefore the output voltage is equal to , $v_0 = V_m \cdot \sin \omega t + V_m$                                                                                        |                    |

|      | <ul> <li>Thus a d.c voltage equal to V<sub>m</sub> is added to input signal. It causes the waveform to<br/>clamp positively at 0 V.</li> </ul>                                  |                    |

| С    | A JFET has $I_{Dss}$ = 10 mA, $V_P$ = $-5$ volts, gmo = 2 ms. Calculate the trans-conductance and                                                                               | 4M                 |

|      | drain current of the JFET for $V_{Gs} = -2.5$ volts.                                                                                                                            |                    |

| Ans: | The expression for drain current ID, in the saturation region is,                                                                                                               |                    |

|      | $I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2$                                                                                                                         |                    |

|      | ( V <sub>P</sub> )                                                                                                                                                              | Formula            |

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

## **SUMMER-18 EXAMINATION**

**Subject Name: Basic Electronics**

**Model Answer**

|   | $=10*10^{-3}\left(1-\frac{-2.5}{-5}\right)^2$                                                      | 1M each                      |

|---|----------------------------------------------------------------------------------------------------|------------------------------|

|   | =2.5mA                                                                                             | Correct<br>answer-1M<br>each |

|   | $g_m = \frac{I_D}{V_{GS}}$                                                                         | Cacii                        |

|   | $gm = \left  \frac{2.5}{-2.5} \right $                                                             |                              |

|   | gm=1ʊ                                                                                              |                              |

|   | (or)                                                                                               |                              |

|   | $g_m = g_{mo} \sqrt{\frac{I_D}{I_{DSS}}}$                                                          |                              |

|   | $gm = 2*\sqrt{\left(\frac{2.5}{10}\right)}$                                                        |                              |

|   | gm=1ʊ                                                                                              |                              |

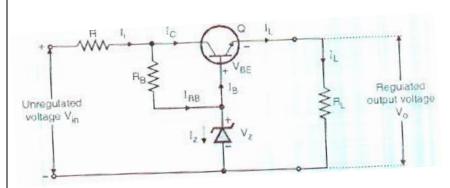

| d | Draw, the circuit diagram for transistor series regulator and explain functions of each component. | 4M                           |

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

## **SUMMER-18 EXAMINATION**

**Subject Name: Basic Electronics Model Answer**

Subject Code: 22216

## Ans:

Transistor (Q)- It acts as a control element and it is connected in series with the load resistor R<sub>L</sub>. It also acts as a variable resistor to control the output voltage.

Zener Diode- It provides reference voltage.

Resistor (R)- It acts as a current limiting resistor.

Base Resistor (R<sub>B</sub>)-It provides biasing for transistor Q to keep the transistor in active region.

Diagram-2M

**Function of** component-2M

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

## **SUMMER-18 EXAMINATION**

**Subject Name: Basic Electronics**

**Model Answer**

| Q.<br>No. | Sub<br>Q.<br>N. | Answers                                                                |                               |                                             |                                | Markin<br>g<br>Scheme                                                      |

|-----------|-----------------|------------------------------------------------------------------------|-------------------------------|---------------------------------------------|--------------------------------|----------------------------------------------------------------------------|

| 4         |                 | Attempt any THREE:                                                     |                               |                                             |                                | 12-<br>Total<br>Marks                                                      |

|           | а               | (ii) Rectification e                                                   | ode used in circu             | uit.                                        | ave rectifiers :               | 4M                                                                         |

|           | Ans:            | Parameters  No of diodes  Rectification Efficiency  TUF  Ripple factor | Half wave  1 40.6% 0.287 1.21 | Full wave Center-tapped 2 81.2% 0.693 0.482 | Bridge  4  81.2%  0.812  0.482 | 1M each                                                                    |

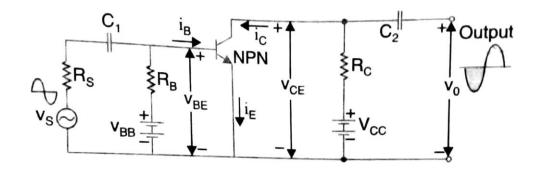

|           | b<br>Ans:       | Operation of NPN transistor in Active region is one in which ba        | VBE -T IB                     | B LE VCE                                    | base collector junction will   | 4M Diagram- 2M Operation-2M Note: Any other configur ation can be consider |

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

# **SUMMER-18 EXAMINATION**

**Subject Name: Basic Electronics Model Answer**

|      | be reverse biased in a transistor.                                                                                                                                                                               | ed      |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|      | Due to forward bias at base emitter junction, the barrier potential is reduced and results in electron flow from emitter to base or current $I_E$ .                                                              |         |

|      | Some of the electrons entering base region will combine with holes in the base region and result in base current $I_{\text{B}}$ .                                                                                |         |

|      | Remaining large number of electrons will pass to the collector circuit and represent the collector current $I_{\text{c}}$                                                                                        |         |

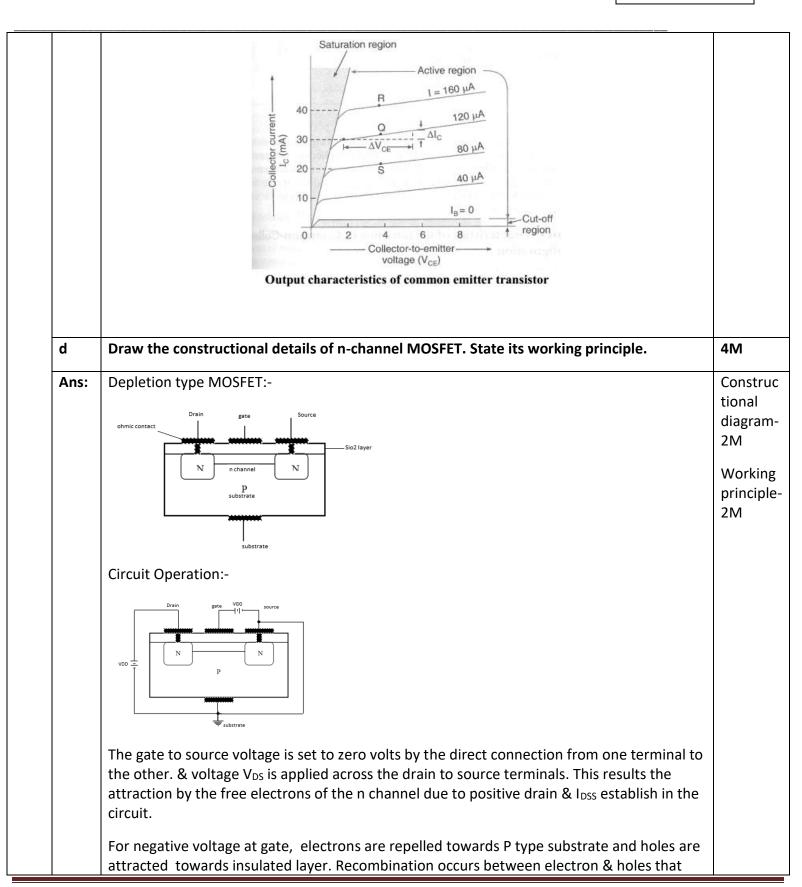

|      | In the active region, the collector current increases slightly(nearly constant) as collector-emitter voltage $V_{CE}$ increases. The value of the collector current $I_C$ increases with the increase in $I_B$ . |         |

|      | In the active region $I_C = \beta I_{B.}$                                                                                                                                                                        |         |

| С    | Draw the input and output characteristics of CE configuration with proper labelling of various regions.                                                                                                          | 4M      |

| Ans: |                                                                                                                                                                                                                  | 2M each |

|      | $V_{CE} = 1V$ $V_{CE} = 2V$ $V_{CE} = 20V$                                                                                                                                                                       |         |

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

#### **SUMMER-18 EXAMINATION Subject Name: Basic Electronics Model Answer**

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

## **SUMMER-18 EXAMINATION**

**Subject Name: Basic Electronics**

**Model Answer**

Subject Code: 22216

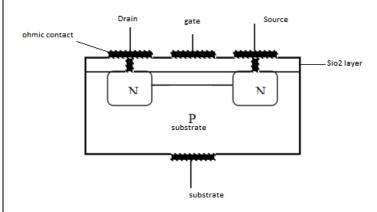

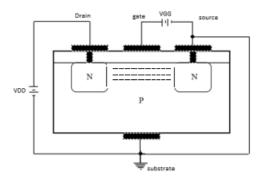

will reduce the number of free electrons in the channel for conduction. So drain current reduces. The value of V<sub>GS</sub> at which drain current is nearly equal to zero is called cut off voltage.

When gate is positive with respect to source, then positive V<sub>GS</sub> draws additional electrons from the P type substrate. Thus drain current (ID) increases as increase in positive VGS.

OR

Enhancement - Type MOSFET:-

## Circuit Operation:

In fig. both V<sub>GS</sub> & V<sub>DS</sub> have been set at positive with respect to the source. The positive potential at the gate will attract the electrons from the P substrate & accumulate in the region near to the surface of SiO<sub>2</sub> layer. The SiO<sub>2</sub> layer & its insulating qualities will prevent the negative carriers (i.e. electrons) from being absorbed at the gate.

As V<sub>GS</sub> increases, the concentration of electrons near the SiO<sub>2</sub> surface increases & there is formation of channel & the current starts following through the circuit for further applied voltage.

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

## **SUMMER-18 EXAMINATION**

**Subject Name: Basic Electronics**

**Model Answer**

| е    | Describe the working of zener as a voltage regulator.                                                                                                                                                                                                                        | 4M                           |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Ans: | Unregulated voltage  V <sub>1</sub> V <sub>2</sub> V <sub>3</sub> V <sub>4</sub> V <sub>7</sub> Regulated voltage                                                                                                                                                            | Diagra<br>2M<br>Workii<br>2M |

|      | Zener regulator                                                                                                                                                                                                                                                              |                              |

|      | Working                                                                                                                                                                                                                                                                      |                              |

|      | For proper operation, the input voltage $V_i$ must be greater than the Zener voltage $V_z$ . This ensures that the Zener diode operates in the reverse breakdown condition. The unregulated input voltage $V_i$ is applied to the Zener diode.                               |                              |

|      | Suppose this input voltage exceeds the Zener voltage. This voltage operates the Zener diode in reverse breakdown region and maintains a constant voltage across the load inspite of input AC voltage fluctuations or load current variations. The input current is given by, |                              |

|      | $I_S = (V_i - V_z) / R_s = (V_i - V_{o)} / R_s$                                                                                                                                                                                                                              |                              |

|      | We know that the input current $I_S$ is the sum of Zener current $I_Z$ and load current $I_L$ .                                                                                                                                                                              |                              |

|      | Therefore, $I_S = I_z + I_L$ or $I_z = I_S - I_L$                                                                                                                                                                                                                            |                              |

|      | As the load current increase, the Zener current decreases so that the input current remains                                                                                                                                                                                  |                              |

|      | constant. According to Kirchhoff's voltage law, the output voltage is given by,                                                                                                                                                                                              |                              |

|      | $V_0 = V_i - I_s$ . $R_s$                                                                                                                                                                                                                                                    |                              |

|      | As the input current is constant, the output voltage remains constant. The reverse would be                                                                                                                                                                                  |                              |

|      | true, if the load current decreases. This circuit is also correct for the changes in input voltage.                                                                                                                                                                          |                              |

|      | As the input voltage increases, more Zener current will flow through the Zener diode. This                                                                                                                                                                                   |                              |

|      | increases the input voltage Is, and also the voltage drop across the resistor Rs, but the load                                                                                                                                                                               |                              |

|      | voltage Vo would remain constant. The reverse would be true, if the decrease in input voltage is not below Zener voltage.                                                                                                                                                    |                              |

|      | Thus, a Zener diode acts as a voltage regulator and the fixed voltage is maintained across the load resistor R <sub>L</sub> .                                                                                                                                                |                              |

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

# **SUMMER-18 EXAMINATION**

**Subject Name: Basic Electronics Model Answer**

| Q.<br>No. | Sub<br>Q.<br>N. | Answers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Marking<br>Scheme           |

|-----------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 5         |                 | Attempt any TWO:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12- Total<br>Marks          |

|           | а               | Explain drain characteristics of JFET with ohmic region, saturation region, cut-off region and break down region.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6M                          |

|           | Ans:            | Ohmic region  Pinch-off or Saturation region  Note that the state of t | 3 Marks for characteristics |

|           |                 | The drain characteristics of JFET can be explained as follows:  Ohmic Region:  This region is represented by curve OA in the figure. In this region, the drain current increases linearly with the increase in drain-to-source voltage, obeying Ohm's law. The linear increase in drain current is due to the fact that N-type semiconductor bar acts like a simple resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                             |

|           |                 | Curve AB:  In this region, the drain current increases at the reverse square law rate with the increase in drain-to-source voltage. It means that drain current increases slowly as compared to that in ohmic region. It is because of the fact, that with the increase in drain-to-source voltage, the drain current increases. This in turn increases the reverse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 Mark for<br>Each region   |

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

## **SUMMER-18 EXAMINATION**

**Subject Name: Basic Electronics**

**Model Answer**

Subject Code: 22216

bias voltage across the gate-source junction. As a result of this, the depletion region grows in size, thereby reducing the effective width of channel. At the drain-to-source voltage, corresponding to point B, the channel width is reduced to a minimum value and is known as pinch off. The drain-to-source voltage, at which the channel pinch-off occurs is known as pinch-off voltage (V<sub>p</sub>)

### Pinch off region:

This region is shown by the curve BC. It is also called saturation region or constant current region. Here the drain current remains constant at its maximum value (i.e. IDSS). The drain, current in the pinch off region, depends upon the gate-to-source voltage and is given by the relation

$$I_D = I_{DSS}(1 - \frac{V_{GS}}{V_p})^2$$

The above relation is known as Shockley's equation. The pinch off region is the normal operating region of JFET, when used as an amplifier.

## Breakdown region:

This region is shown by the curve CD. In this region, the drain current increases rapidly as the drain-to-source voltage are increased. It happens because of the breakdown of gate-to-source junction due to avalanche effect. The drain-to-source voltage corresponding to point C is called breakdown voltage.

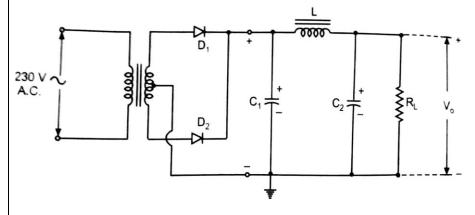

Draw circuit diagram and input and output waveforms of full wave rectifier b connected with  $\pi$  filter.

**6M**

#### Ans:

Circuit diagram of full wave rectifier connected with  $\pi$  filter:

3Marks for Circuit diagram

Input and Output waveforms of full wave rectifier connected with  $\pi$  filter

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

# **SUMMER-18 EXAMINATION**

**Subject Name: Basic Electronics Model Answer**

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

# SUMMER- 18 EXAMINATION

Subject Name: Basic Electronics Model Answer Subject Code: 22216

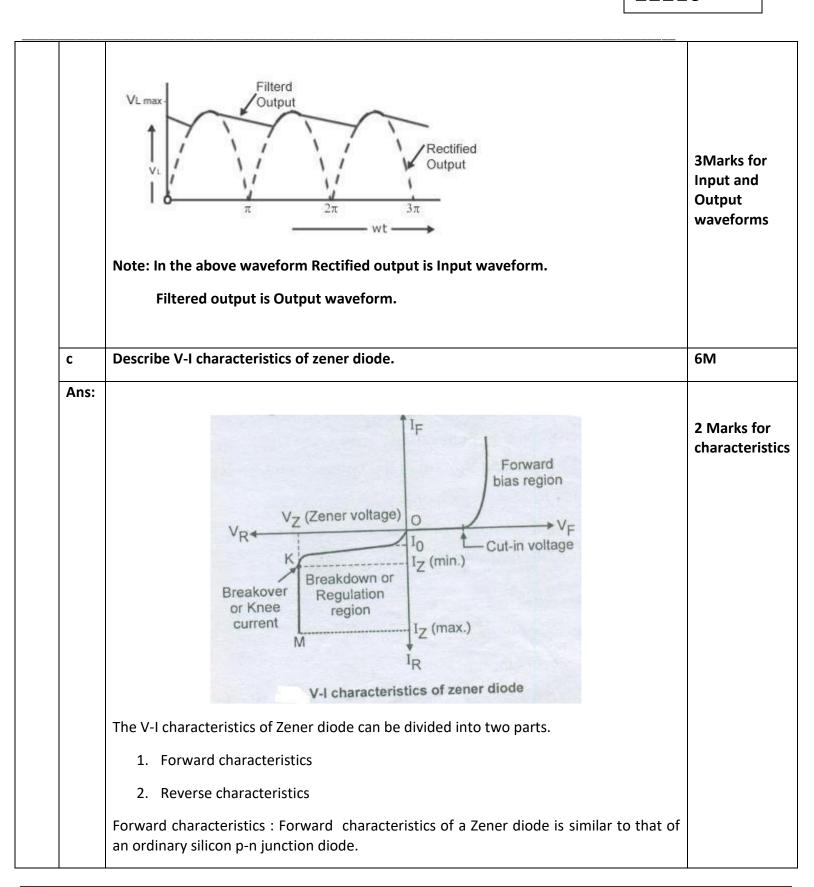

|          |                                                                         | It indicates that forward current is very small for voltages below knee (cut-in) voltage and large for voltages above knee voltage.  Reverse characteristics: Zener diode is silicon p-n junction device which differs from a rectifier diode, in the sense, that it is operated in the reverse breakdown region.  When the reverse voltage across a diode is increased a critical voltage called breakdown voltage, the reverse current increases sharply as shown in the curve KM. This is an indication that the breakdown has occurred. This breakdown voltage is called as Zener breakdown voltage or Zener voltage and it is denoted by Vz.  The breakdown voltage of Zener diode is set by carefully controlling the doping level during manufacture.  After breakdown has occurred, the voltage across Zener diode remains constant equal to Vz. Any increase in the source voltage will result in the increase in reverse Zener current. | 4 Marks for description     |

|----------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Q.<br>No | Sub<br>Q.<br>N.                                                         | Answers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Marking<br>Scheme           |

| 6        |                                                                         | Attempt any TWO:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12- Total<br>Marks          |

|          | a Show constructional details of LED. Give any two applications of LED. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6M                          |

|          | Ans:                                                                    | Constructional details of LED:  A pn junction diode, which emits light when forward biased, is known as a light emitting diode (LED). This emitted light may be visible or invisible. The amount of light output is directly proportional to the forward current. Thus higher the forward current, higher is the light output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2 Marks for<br>Construction |

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

## **SUMMER-18 EXAMINATION**

**Subject Name: Basic Electronics**

**Model Answer**

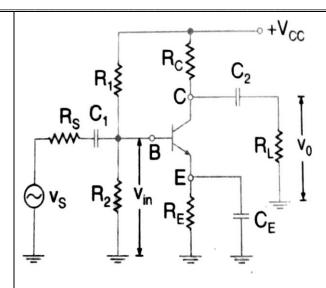

| Ans | Single stage CE amplifier Circuit diagram:                                                                       | 3 Marks                      |  |  |

|-----|------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|

| b   | Describe the working of single stage CE amplifier with neat circuit diagram.                                     | 6M                           |  |  |

|     | 10. Used in aviation lighting, automotive lighting, advertising and general lighting                             |                              |  |  |

|     | 9. Used for traffic signal management                                                                            |                              |  |  |

|     |                                                                                                                  |                              |  |  |

|     | <ul><li>7. It is used in burglar alarm systems.</li><li>8. It is used to indicate digital logic state.</li></ul> |                              |  |  |

|     | 6. It is used in optical switching applications.                                                                 |                              |  |  |

|     |                                                                                                                  |                              |  |  |

|     |                                                                                                                  | 2 Marks<br>any 2<br>Applicat |  |  |

|     | 4. It is used in 7- segment, 16- segment, alphanumeric displays.                                                 |                              |  |  |

|     | It is used in optical communication systems.  3. It is used in infrared remote control.                          |                              |  |  |

|     | It is used in optical communication systems.                                                                     |                              |  |  |

|     | It is used in opto couplers.                                                                                     |                              |  |  |

|     | Active region  Active region  n-region  Anode  Cathode  Applications of LED:                                     | 2 Marks<br>diagram<br>one )  |  |  |

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

# **SUMMER-18 EXAMINATION**

**Subject Name: Basic Electronics Model Answer**

Subject Code: 22216

(OR)

## Working of single stage CE amplifier:

The circuit diagram of a voltage amplifier using single transistor in CE configuration is shown in above figure.

It is also known as a small-signal single-stage CE amplifier or RC coupled CE amplifier. It is also known as a voltage amplifier.

- The input a.c. signal is applied across the base emitter terminals of the transistor & output is taken across collector emitter terminals of the transistor.

- The potential divider biasing is provided by resistors R<sub>1</sub>, R<sub>2</sub> and R<sub>E</sub>. It provides good stabilization of the operating point.

- The capacitors C<sub>1</sub> and C<sub>2</sub> are called the coupling capacitors used to passes the AC voltage signals from one side to the other. At the same time, it does not allow the

3 Marks for working

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

## SUMMER- 18 EXAMINATION

Subject Name: Basic Electronics Model Answer Subject Code: 22216

|      | <ul> <li>dc voltage to pass through .Hence it is also known as blocking capacitors.</li> <li>The capacitor C<sub>E</sub> works as a bypass capacitor. It bypasses all the AC currents from the emitter to the ground and avoids the negative current feedback. It increases the output AC voltage.</li> <li>The resistance R<sub>L</sub> represents the resistance of whatever is connected at the output. It may be load resistance or input resistance of the next stage.</li> </ul> |                                                 |                                                                                                                                                                                                 |                                                                                                                                                 |                                                                                |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

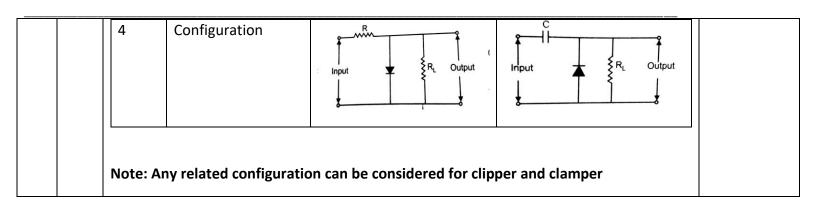

| С    | Differentiate clipper and clamper with following points:  (i) Components used in circuit.  (ii) Function  (iii) Application  (iv) Configuration                                                                                                                                                                                                                                                                                                                                        |                                                 |                                                                                                                                                                                                 |                                                                                                                                                 |                                                                                |

| Ans: | Sr.No.  1  2                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Parameter  Components used in circuit  Function | Clipper  Diode, resistor  To remove a part of input signal voltage above or below a certain level.                                                                                              | Clamper  Diode, resistor, capacitor  To add a DC shift to the input signal                                                                      | 2 Marks for<br>Componen<br>used in                                             |

|      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Application                                     | <ul> <li>Digital computers,</li> <li>radars,</li> <li>radio and television receivers,</li> <li>to limit the amplitude of the input signal voltages required in several applications.</li> </ul> | <ul> <li>Used in Television receivers to restore the original dc reference signal to the video signal,</li> <li>voltage multipliers.</li> </ul> | circuit  1 Mark for Function  1 Mark for Application  2 Mark for Configuration |

(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

## **SUMMER-18 EXAMINATION**

**Subject Name: Basic Electronics**

**Model Answer**