(Autonomous) (ISO/IEC - 27001 - 2013 Certified)

#### <u>MODEL ANSWER</u> WINTER– 18 EXAMINATION

**Subject Title:** Digital Techniques

**Subject Code:**

22320

#### **Important Instructions to examiners:**

- 1) The answers should be examined by key words and not as word-to-word as given in the model answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may try to assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given more Importance (Not applicable for subject English and Communication Skills.

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figures drawn by candidate and model answer may vary. The examiner may give credit for any equivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constant values may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent concept.

| Q.<br>No. | Sub<br>Q.N. | Answer                                                                 | Marking<br>Scheme |

|-----------|-------------|------------------------------------------------------------------------|-------------------|

| Q.1       |             | Attempt any FIVE of the following:                                     | Total Marks<br>10 |

|           | a)          | Write the radix of binary,octal,decimal and hexadecimal number system. | 2M                |

|           | Ans:        | Radix of: Binary – 2 Octal - 8 Decimal - 10                            | ½ M each          |

|           |             | Hexadecimal -16                                                        |                   |

|           | b)          | Draw the circuit diagram for AND and OR gates using diodes.            | 2M                |

|           | Ans:        | Diode AND gate :Diode OR gate :                                        | 1 M each          |

| c)         | Write simple example of Boolean expression for SOP and POS.                                                                                                 | 2M                                     |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| Ans:       | $\frac{SOP \text{ form:}}{Y = AB + BC + A\overline{C}}$                                                                                                     | 1 M each<br>(any proper<br>example car |  |

|            | POS form:                                                                                                                                                   | be considered)                         |  |

|            | $Y = (A + B) (B + C) (A + \overline{C})$                                                                                                                    |                                        |  |

| <b>d</b> ) | State the necessity of multiplexer.                                                                                                                         | 2M                                     |  |

| Ans:       | Necessity of Multiplexer:                                                                                                                                   |                                        |  |

|            | It reduces the number of wires required to pass data from source to destination.                                                                            | 2 M(any two<br>proper<br>points)       |  |

|            | For minimizing the hardware circuit.                                                                                                                        |                                        |  |

|            | For simplifying logic design.                                                                                                                               |                                        |  |

|            | • In most digital circuits, many signals or channels are to be transmitted, and then it becomes necessary to send the data on a single line simultaneously. |                                        |  |

|            | <ul> <li>Reduces the cost as sending many signals separately is expensive and<br/>requires more wires to send.</li> </ul>                                   |                                        |  |

|            |                                                                                                                                                             |                                        |  |

| e)         | Draw logic diagram of T flip-flop and give its truth table.                                                                                                 | 2M                                     |  |

| Ans:       | Note: Diagram Using logic gates with proper connection also can be consider.  Logic Diagram:                                                                | 1M (any on<br>diagram)                 |  |

|            | Pr                                                                                                                                                          |                                        |  |

|            | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                       |                                        |  |

|            | $\bar{Q}$                                                                                                                                                   | 1 M                                    |  |

|            | OR $OR$                                                                                                                                                     |                                        |  |

|            | SI CON                                                                                                                                                      |                                        |  |

|            |                                                                                                                                | Input<br>T <sub>n</sub> | Output Q <sub>n+1</sub>             | Operation Performed               |                  |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------|-----------------------------------|------------------|--|--|--|

|            |                                                                                                                                | 0                       | Qn                                  | No change                         |                  |  |  |  |

|            |                                                                                                                                | 1                       | $\overline{\overline{Q}}_n$         | Toggle                            |                  |  |  |  |

| <b>f</b> ) |                                                                                                                                | modulus of a            | counter. Write the n                | umbers of flip flops required for | 2M               |  |  |  |

| Ans:       | Modulus of counter is defined as number of states/clock the counter countes.                                                   |                         |                                     |                                   |                  |  |  |  |

|            | •                                                                                                                              | The numbers             | of flip flops required f            | or Mod-6 counter is 3.            | No. of FF-<br>1M |  |  |  |

| g)         | State fu                                                                                                                       | ınction of pr           | eset and clear in flip f            | lop.                              | 2M               |  |  |  |

|            | • Hence, the function of preset is to set a flip flop i.e. Q = 1 and the function of clear is to clear a flip flop i.e. Q = 0. |                         |                                     |                                   |                  |  |  |  |

|            |                                                                                                                                | 27 17                   | Output                              | Operation performed               |                  |  |  |  |

|            |                                                                                                                                | Inputs                  |                                     | Operation performed               |                  |  |  |  |

|            | CK 1                                                                                                                           | Cr P                    | e Q                                 | (2) B                             |                  |  |  |  |

|            | CK 1 0                                                                                                                         | - 15<br>102             | e Q                                 | Normal FLIP-FLOP Clear            |                  |  |  |  |

|            | 1                                                                                                                              | Cr P                    | $Q$ $Q_{a+1}(\text{Table 7.1})$ $0$ | Normal FLIP-FLOP                  |                  |  |  |  |

|            | 1 0                                                                                                                            | Cr P                    | $Q$ $Q_{a+1}(\text{Table 7.1})$ $0$ | Normal FLIP-FLOP<br>Clear         |                  |  |  |  |

### MAHARASHTRASTATE BOARD OF TECHNICAL EDUCATION (Autonomous)

(ISO/IEC - 27001 - 2013 Certified)

| <b>b</b> ) | Convert – $(255)_{10} = (?)_{16} = (?)_8$                                                                                                                                                                                                                               | 4M  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Ans:       | (157) <sub>10</sub> = (?) <sub>BCD</sub> = (?) <sub>Excess3</sub><br>(i) (255) <sub>10</sub> = (FF) <sub>16</sub> = (377) <sub>8</sub><br>(255) <sub>10</sub> = (FF) <sub>16</sub><br>$16 \mid 255 \mid F \mid$ | 1 M |

|            | $(255)_{10} = (377)_{8}$ $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                          | 1 M |

|            | (ii) $(157)_{10} = (000101010111)_{BCD} = (010010001010)_{Excess3}$                                                                                                                                                                                                     |     |

|            | $(157)_{10} = (000101010111)_{BCD}$ $\frac{1}{0001} \frac{5}{0101} \frac{7}{0111}$                                                                                                                                                                                      | 1 M |

|            | (000101010111) <sub>BCD</sub> = (010010001010) <sub>Excess3</sub> 11 111 111 0001 0101 0111 + 0011 0011                                                                                                                                                                 | 1 M |

| c)         | Draw the symbol, truth table and logic expression of any one universal logic gate. Write reason why it is called universal gate.                                                                                                                                        | 4M  |

| Ans:       | (Note: Any one universal gate has to be considered.) Universal Gates: NAND or NORSymbol:                                                                                                                                                                                | 1 M |

|            | Truth table:  A B Y O O 1 O 1 O 1 O 1 O 1 O 1 O 1 O 1 O 0 D 1 O O 0 D 1 O O O O O O O O O O O O O O O O O O                                                                                                                                                             | 1 M |

|            | $Y = \overline{A \cdot B}$ $Y = (\overline{A + B})$                                                                                                                                                                                                                     | 1 M |

|            | NAND and NOR gates are called as "Universal Gate" as it is possible to implement any Boolean expression using these gates.                                                                                                                                              | 1 M |

### MAHARASHTRASTATE BOARD OF TECHNICAL EDUCATION (Autonomous)

(ISO/IEC - 27001 – 2013 Certified)

| Q. 3 |            | <b>Attempt any THREE:</b>                                                         |                                    |                            | 12-Total    |

|------|------------|-----------------------------------------------------------------------------------|------------------------------------|----------------------------|-------------|

|      | a)         | Compare TTL and CM (i) Propagation (ii) Power Dissi (iii) Fan-out (iv) Basic gate | •                                  | pasis of following:        | Marks<br>4M |

|      | Ans:       | <u>NOTE :- ( Rel</u>                                                              | levant points of comparison- 1     | M for each point)          | 1 Marks     |

|      |            | Parameter                                                                         | CMOS                               | TTL                        | each point  |

|      |            | Propagation delay                                                                 | 70-105 nsec/more than TTL          | 10 nsec/Less than<br>CMOS  |             |

|      |            | Power Dissipation                                                                 | Less 0.1 mW/Less than TTL          | More 10 mW/ More than CMOS |             |

|      |            | Fan-out                                                                           | 50/More than TTL                   | 10/Less than CMOS          |             |

|      |            | Basic gate                                                                        | NAND/NOR                           | NAND                       |             |

| =    | <b>b</b> ) | Describe the function simplification and logi                                     | of full Adder Circuit using        | its truth table, K-Map     | 4M          |

|      |            | Block diagram :  FULL ADDER                                                       | bits A and B, and carry C for Cour | tom the previous oit.      | 1M          |

|      |            |                                                                                   |                                    |                            | 1M          |

(Autonomous) (ISO/IEC - 27001 – 2013 Certified)

#### **Truth Table:**

|   | Input |     | Out | put   |

|---|-------|-----|-----|-------|

| Α | В     | Cin | Sum | Carry |

| 0 | 0     | 0   | 0   | 0     |

| 0 | 0     | 1   | 1   | 0     |

| 0 | 1     | 0   | 1   | 0     |

| 0 | 1     | 1   | 0   | 1     |

| 1 | 0     | 0   | 1   | 0     |

| 1 | 0     | 1   | 0   | 1     |

| 1 | 1     | 0   | 0   | 1     |

| 1 | 1     | 1   | 1   | 1     |

**1M**

**1M**

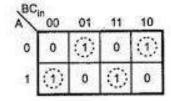

**K-Map :-**

For Carry (Cout)

For Sum

$C_{out} = AB+A C_{in}+B C_{in}$  Sum =  $\overline{A} \overline{B} C_{in}+\overline{A} \overline{B} \overline{C}_{in}+A \overline{B} \overline{C}_{in}+AB C_{in}$

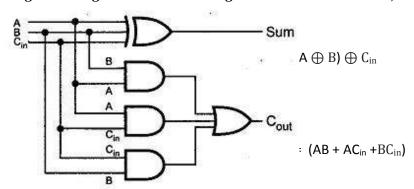

#### **Logic Diagram:**

(Note: Logic Diagram using basic or universal gate also can be consider)

| c)   | Realize the basic logic gates, NOT, OR and AND gates using NOR gates only.   | 4M   |  |  |  |  |

|------|------------------------------------------------------------------------------|------|--|--|--|--|

| Ans: |                                                                              | 13.7 |  |  |  |  |

|      | ( NOT GATE USING NOR GATE:1 M )                                              | 1M   |  |  |  |  |

|      | A————×                                                                       |      |  |  |  |  |

|      | where, $X = A$ NOR A $x = \overline{A}$                                      |      |  |  |  |  |

|      | (AND GATE USING NOR GATE:1.5 MARKS)                                          |      |  |  |  |  |

|      |                                                                              | 1.5M |  |  |  |  |

|      | $\overline{Q} = \overline{A} + \overline{B} = \overline{A} + \overline{B}$   |      |  |  |  |  |

|      |                                                                              |      |  |  |  |  |

|      | =A.B<br>= <b>A.B</b>                                                         |      |  |  |  |  |

|      | (OR GATE USING NOR GATE:1.5 MARKS)                                           |      |  |  |  |  |

|      |                                                                              |      |  |  |  |  |

|      |                                                                              |      |  |  |  |  |

|      |                                                                              |      |  |  |  |  |

|      | $Q = \overline{A + B}$                                                       |      |  |  |  |  |

|      | $=\mathbf{A}+\mathbf{B}$                                                     |      |  |  |  |  |

|      |                                                                              |      |  |  |  |  |

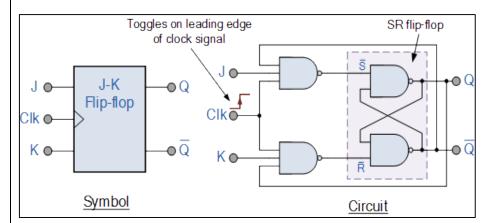

| d)   | Describe the working of JK flip-flop with its truth table and logic diagram. | 4M   |  |  |  |  |

| Ans: | (Diagram-2 M, Working-1M, Truth table-1M)                                    |      |  |  |  |  |

|      | Truth Table :-                                                               | 1M   |  |  |  |  |

|      | Truth Table                                                                  |      |  |  |  |  |

|      | J K CLK Q                                                                    |      |  |  |  |  |

|      | 0 0 † Q <sub>0</sub> (no change)                                             |      |  |  |  |  |

|      |                                                                              |      |  |  |  |  |

|      | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                        |      |  |  |  |  |

|      |                                                                              |      |  |  |  |  |

|      |                                                                              |      |  |  |  |  |

$\begin{array}{c} (Autonomous) \\ (ISO/IEC - 27001 - 2013 \; Certified) \end{array} \\$

#### Diagram:-

**2M**

#### **Working:**-

The **JK flip flop** is basically a gated SR flip-flop with the addition of a clock input circuitry that prevents the illegal or invalid output condition that can occur when both inputs S and R are equal to logic level "1". Due to this additional clocked input, a JK flip-flop has four possible input combinations, "logic 1", "logic 0", "no change" and "toggle".

**1M**

Both the S and the R inputs of the previous SR bistable have now been replaced by two inputs called the J and K inputs, respectively after its inventor Jack Kilby. Then this equates to: J = S and K = R.

The two 2-input AND gates of the gated SR bistable have now been replaced by two 3-input NAND gates with the third input of each gate connected to the outputs at Q and Q. This cross coupling of the SR flip-flop allows the previously invalid condition of S = "1" and R = "1" state to be used to produce a "toggle action" as the two inputs are now interlocked.

If the circuit is now "SET" the J input is inhibited by the "0" status of Q through the lower NAND gate. If the circuit is "RESET" the K input is inhibited by the "0" status of Q through the upper NAND gate. As Q and Q are always different we can use them to control the input. When both inputs J and K are equal to logic "1", the JK flip flop toggles

| Q. 4 | A)   | Attempt any THREE of the following:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12-Total<br>Marks |

|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|      | a)   | Draw and explain working of 4 bit serial Input parallel Output shift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4M                |

|      |      | register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |

|      | Ans: | (Diagram:2M,Explaination:2M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |

|      |      | Diagram :-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

|      |      | 4-bit Parallel Data Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2M                |

|      |      | $Q_A$ $Q_B$ $Q_C$ $Q_D$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |

|      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

|      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

|      |      | Serial D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q D C Q |                   |

|      |      | Data in FFA FFB FFC FFD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |

|      |      | CLK CLK CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

|      |      | CLR CLR CLR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

|      |      | Clear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |

|      |      | Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                   |

|      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

|      |      | Explaination:-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |

|      |      | If a logic "1" is connected to the DATA input pin of FFA then on the first                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

|      |      | clock pulse the output of FFA and therefore the resulting Q <sub>A</sub> will be set HIGH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2M                |

|      |      | to logic "1" with all the other outputs still remaining LOW at logic "0".  Assume now that the DATA input pin of FFA has returned LOW again to logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2111              |

|      |      | "0" giving us one data pulse or 0-1-0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

|      |      | The second clock pulse will change the output of FFA to logic "0" and the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |

|      |      | output of FFBand Q <sub>B</sub> HIGH to logic "1" as its input D has the logic "1" level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |

|      |      | on it from Q <sub>A</sub> . The logic "1" has now moved or been "shifted" one place along                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |

|      |      | the register to the right as it is now at Q <sub>A</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

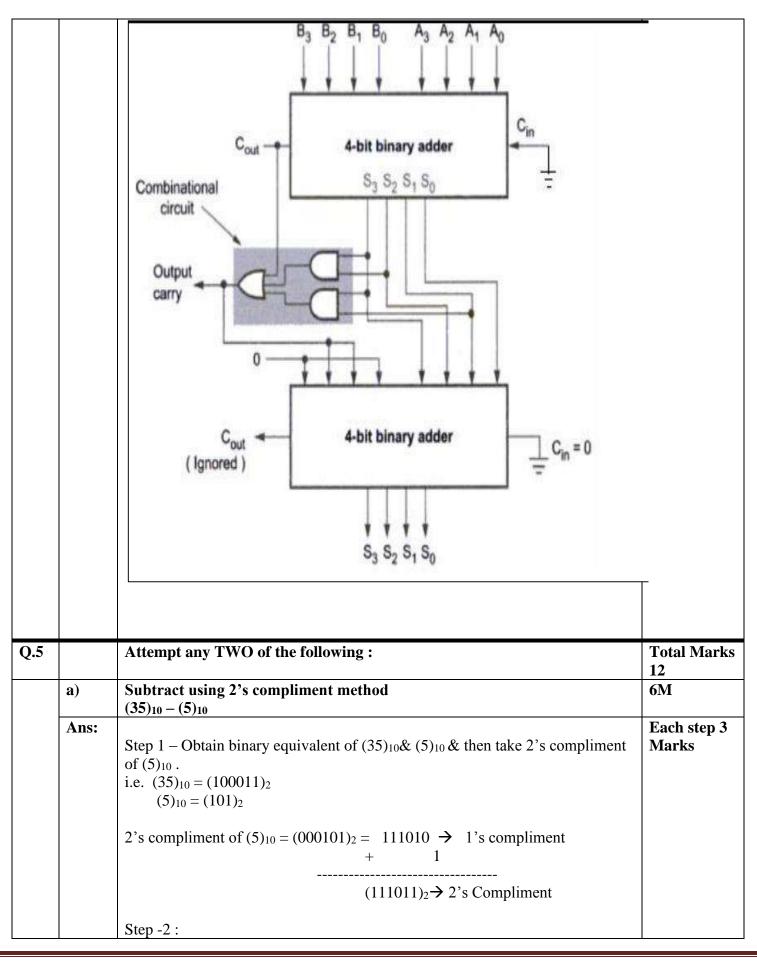

|      |      | When the third clock pulse arrives this logic "1" value moves to the output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |