# SUMMER-19 EXAMINATION Model Answer

Subject Code:

22320

#### **Important Instructions to examiners:**

- 1) The answers should be examined by key words and not as word-to-word as given in themodel answer scheme.

- 2) The model answer and the answer written by candidate may vary but the examiner may tryto assess the understanding level of the candidate.

- 3) The language errors such as grammatical, spelling errors should not be given moreImportance (Not applicable for subject English and Communication Skills.

- 4) While assessing figures, examiner may give credit for principal components indicated in the figure. The figures drawn by candidate and model answer may vary. The examiner may give credit for any equivalent figure drawn.

- 5) Credits may be given step wise for numerical problems. In some cases, the assumed constantvalues may vary and there may be some difference in the candidate's answers and model answer.

- 6) In case of some questions credit may be given by judgement on part of examiner of relevant answer based on candidate's understanding.

- 7) For programming language papers, credit may be given to any other program based on equivalent concept.

| Q.<br>No. | Sub<br>Q. N. | Answers                                |                  |                     |             |    |  |  |

|-----------|--------------|----------------------------------------|------------------|---------------------|-------------|----|--|--|

| 1         | (A)          | (A) Attempt any FIVE of the following: |                  |                     |             |    |  |  |

|           | (a)          | List the binary,octal and              | hexadecimal numb | ers for decimal no. | 0 to 15     | 2M |  |  |

|           | Ans:         |                                        |                  |                     |             | 2M |  |  |

|           |              | DECIMAL                                | BINARY           | OCTAL               | HEXADECIMAL |    |  |  |

|           |              | 0                                      | 0000             | 0                   | 0           |    |  |  |

|           |              | 1                                      | 0001             | 1                   | 1           |    |  |  |

|           |              | 2                                      | 0010             | 2                   | 2           |    |  |  |

|           |              | 3                                      | 0011             | 3                   | 3           |    |  |  |

|           |              | 4                                      | 0100             | 4                   | 4           |    |  |  |

|           |              | 5                                      | 0101             | 5                   | 5           |    |  |  |

|           |              | 6                                      | 0110             | 6                   | 6           |    |  |  |

|           |              | 7                                      | 0111             | 7                   | 7           |    |  |  |

|           |              | 8                                      | 1000             | 10                  | 8           |    |  |  |

# SUMMER-19 EXAMINATION Model Answer

\_Subject Code:

|     | ı u                                                                                                            | 1001                               | 11                                                                                               | 9                                                | l                   |

|-----|----------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------|

|     | 9                                                                                                              |                                    |                                                                                                  |                                                  |                     |

|     | 10                                                                                                             | 1010                               | 12                                                                                               | A                                                |                     |

|     | 11                                                                                                             | 1011                               | 13                                                                                               | В                                                |                     |

|     | 12                                                                                                             | 1100                               | 14                                                                                               | С                                                |                     |

|     | 13                                                                                                             | 1101                               | 15                                                                                               | D                                                |                     |

|     | 14                                                                                                             | 1110                               | 16                                                                                               | E                                                |                     |

|     | 15                                                                                                             | 1111                               | 17                                                                                               | F                                                |                     |

| (b) | Define fan-in and fan-or                                                                                       | ut of a gate.                      |                                                                                                  |                                                  | 2M                  |

|     | some have more than tw                                                                                         | efines the maximun                 | n number of digital ir                                                                           | nputs that the output                            | 10                  |

|     | single logic gate can fee                                                                                      | d. Most transistor-t               | ransistor logic ( TTL )                                                                          | gates can reed up to .                           | <sup>⊥</sup> ∪   1M |

|     | single logic gate can feed other digital gates.                                                                | d. Most transistor-t               | ransistor logic ( TTL )                                                                          | gates can reed up to                             | 10   1M             |

| (c) |                                                                                                                |                                    |                                                                                                  |                                                  | 1M 2M               |

|     | other digital gates.                                                                                           |                                    |                                                                                                  |                                                  | 1141                |

| (c) | other digital gates.                                                                                           |                                    |                                                                                                  |                                                  | 1141                |

|     | other digital gates.  Compare between sync                                                                     | hronous and asynd                  | chronous counter (ar                                                                             | ny two points).                                  | 1141                |

|     | Compare between sync                                                                                           | hronous and asyno                  | Asynchrono                                                                                       | ny two points).<br>us Counter                    | 2M Any              |

|     | Synchronous C All flip flops are                                                                               | hronous and asyno                  | Asynchrono Different cloc                                                                        | us Counter k is applied to                       | 2M Any 1M for e     |

|     | Compare between sync                                                                                           | hronous and asyno                  | Asynchrono                                                                                       | us Counter k is applied to                       | 2M Any              |

|     | Synchronous C All flip flops are with same clock                                                               | counter<br>triggered               | Asynchrono Different cloc different flip                                                         | us Counter k is applied to                       | 2M Any 1M for e     |

|     | Synchronous ( All flip flops are with same clock It is faster.                                                 | Counter triggered                  | Asynchrono Different cloc different flip                                                         | us Counter k is applied to flops.                | 2M Any 1M for e     |

|     | Synchronous C All flip flops are with same clock It is faster. Design is comple Decoding errors                | Counter triggered ex. not present. | Asynchrono Different cloc different flip It is lower I Design is re Decoding erro                | us Counter k is applied to flops. latively easy. | 2M Any 1M for e     |

|     | Synchronous C All flip flops are with same clock It is faster. Design is comple                                | Counter triggered ex. not present. | Asynchrono Different cloc different flip It is lower I Design is re Decoding erro                | us Counter k is applied to flops.                | 2M Any 1M for e     |

|     | Synchronous C All flip flops are with same clock It is faster. Design is compl Decoding errors Any required se | Counter triggered ex. not present. | Asynchrono Different cloc different flip It is lower I Design is re Decoding erro Only fixed sec | us Counter k is applied to flops. latively easy. | 2M Any 1M for e     |

|     | Synchronous C All flip flops are with same clock It is faster. Design is compl Decoding errors Any required se | Counter triggered ex. not present. | Asynchrono Different cloc different flip It is lower I Design is re Decoding erro Only fixed sec | us Counter k is applied to flops. latively easy. | 2M Any 1M for e     |

|     | Synchronous C All flip flops are with same clock It is faster. Design is compl Decoding errors Any required se | Counter triggered ex. not present. | Asynchrono Different cloc different flip It is lower I Design is re Decoding erro Only fixed sec | us Counter k is applied to flops. latively easy. | 2M Any 1M for e     |

# SUMMER-19 EXAMINATION Model Answer

Subject Code:

| (d)  | State two specification of DAC.                                                                                                                                                                                                                                                                                                                                                                                              | 2M   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Ans: | 1.Resolution:                                                                                                                                                                                                                                                                                                                                                                                                                | Any  |

|      | <b>Resolution</b> is defined as the ratio of change in analog output voltage resulting from a change of 1 LSB at the digital input VFS is defined as the full scale analog output                                                                                                                                                                                                                                            | two, |

|      | voltage i.e. the analog output voltage when all the digital input with all digits 1.<br>Resolution = VFS $/(2n-1)$                                                                                                                                                                                                                                                                                                           | each |

|      | 2. Accuracy: Accuracy indicates how close the analog output voltage is to its theoretical value. It indicates the deviation of actual output from the theoretical value. Accuracy depends on the accuracy of the resistors used in the ladder, and the precision of the reference voltage used. Accuracy is always specified in terms of percentage of the full scale output that means maximum output voltage 3. Linearity: |      |

|      | The relation between the digital input and analog output should be linear.  However practically it is not so due to the error in the values of resistors used for the resistive networks.                                                                                                                                                                                                                                    |      |

|      | 4. Temperature sensitivity:                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|      | The analog output voltage of D to A converter should not change due to changes in temperature.                                                                                                                                                                                                                                                                                                                               |      |

|      | But practically the output is a function of temperature. It is so because the resistance values and OPAMP parameters change with changes in temperature.                                                                                                                                                                                                                                                                     |      |

|      | 5. Settling time:  The time required to settle the analog output within the final value, after the change in digital input is called as settling time.                                                                                                                                                                                                                                                                       |      |

|      | The settling time should be as short as possible.  6. Long term drift                                                                                                                                                                                                                                                                                                                                                        |      |

|      | Long term drift are mainly due to resistor and semiconductor aging and can affect all the characteristics.                                                                                                                                                                                                                                                                                                                   |      |

|      | Characteristics mainly affected are linearity, speed etc.  7. Supply rejection                                                                                                                                                                                                                                                                                                                                               |      |

|      | Supply rejection indicates the ability of DAC to maintain scale, linearity and other important characteristics when the supply voltage is varied.                                                                                                                                                                                                                                                                            |      |

|      | Supply rejection is usually specified as percentage of full scale change at or near full scale voltage at 250e                                                                                                                                                                                                                                                                                                               |      |

|      | 8. Speed:  It is defined as the time needed to perform a conversion from digital to analog. It is also defined as the number of conversions that can be performed per second.                                                                                                                                                                                                                                                |      |

# SUMMER-19 EXAMINATION Model Answer

Subject Code:

| Q.  | Sub   | Answers                             | Marking   |

|-----|-------|-------------------------------------|-----------|

| No. | Q. N. |                                     | Scheme    |

|     |       |                                     |           |

| 2   |       | Attempt any THREE of the following: | 12- Total |

|     |       |                                     | Marks     |

|     |       |                                     |           |

**SUMMER-19 EXAMINATION**

Subject Name: Digital technique <u>Model Answer</u>

Subject Code:

| a)   | Convert:                                                                                                                                      | 4M   |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | (i) $(AD92.BCA)_{16} = (?)_{10} = (?)_8 = (?)_2$                                                                                              |      |

| Ans: | (AD92.BCA) <sub>16</sub>                                                                                                                      | 1.51 |

|      | = $(10 \times 16^3) + (13 \times 16^2) + (9 \times 16^1) + (2 \times 16^0) + (11 \times 16^{-1}) + (12 \times 16^{-2}) + (10 \times 16^{-3})$ |      |

|      | = 40960 + 3328 + 144 + 2 + 0.6857 + 0.046875 + 0.00244                                                                                        |      |

|      | = (44434.7368) <sub>10</sub>                                                                                                                  | 1M   |

|      |                                                                                                                                               | 1.51 |

|      | (AD92.BCA) <sub>16</sub> =(1010 1101 1001 0010.1011 1100 1010) <sub>2</sub>                                                                   |      |

|      | (AD92.BCA) <sub>16</sub> = (1010 1101 1001 0010.1011 1100 1010) <sub>2</sub>                                                                  |      |

|      | =(001 010 110 110 010 010.101 111 001 010) <sub>2</sub>                                                                                       |      |

|      | =(126622.5712) <sub>8</sub>                                                                                                                   |      |

|      | Note: any other method can be considered.                                                                                                     |      |

| b)   | Simplify the following and realize it                                                                                                         | 4M   |

|      | $Y = A + \overline{A}\overline{B}C + \overline{A}\overline{B}\overline{C} + ABC + \overline{A}\overline{B}$                                   |      |

| Ans: | $Y = A + \overline{A}\overline{B}C + \overline{A}\overline{B}\overline{C} + ABC + \overline{A}\overline{B}$                                   | 4M   |

|      |                                                                                                                                               |      |

|      |                                                                                                                                               |      |

# **SUMMER-19 EXAMINATION Model Answer**

Subject Code:

| Ans: | Noise margin indicates the amount to noise voltage circuit can tolerate at its input for both logic 1 and logic0.                    | 1M each definition |

|------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| с)   | <ul> <li>(i) Noise margin</li> <li>(ii) Power dissipation</li> <li>(iii) Figure of merit</li> <li>(iv) Speed of operation</li> </ul> | 4M                 |

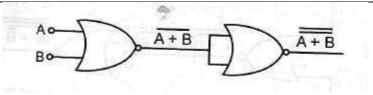

|      | $A \bigcirc \overline{B}$ $B \bigcirc \overline{B}$ $Y = A + \overline{B}$                                                           |                    |

|      | $=(A+\overline{B})$                                                                                                                  |                    |

|      | $= A + \overline{A} \overline{B}$ $= (A + \overline{A}) \cdot (A + \overline{B})$                                                    |                    |

|      | $= A + \overline{A} \overline{B} + \overline{A} \overline{B}$                                                                        |                    |

|      | Y= A+ABC+ABC+AB<br>= A(1+BC)+ABC+AB<br>= A(1+BC)+AB(+Z)+AB                                                                           |                    |

# SUMMER-19 EXAMINATION Model Answer

Subject Code:

|      | the gate.                                                                                                                                        |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | Speed of Operation: Speed of a logic circuit is determined by the time between the application of input and change in the output of the circuit. |    |

| d)   | Draw logic diagram of half adder circuit                                                                                                         | 4M |

| Ans: | A B Sum Carry                                                                                                                                    | 4M |

|      | OR                                                                                                                                               |    |

|      | A B Sum                                                                                                                                          |    |

|      | Note: logic diagram using NAND/NOR also can be considered.                                                                                       |    |

| Q.  | Sub   | Answers                              | Marking   |

|-----|-------|--------------------------------------|-----------|

| No. | Q. N. |                                      | Scheme    |

| _   |       |                                      |           |

| 3   |       | Attempt any THREE of the following : | 12- Total |

|     |       |                                      | Marks     |

|     |       |                                      |           |

# SUMMER-19 EXAMINATION Model Answer

\_Subject Code:

| a)    | Draw the circuit of successive approximation type ADC and explain its working                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4M             |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Ans:  | Offiset voltage = 1/2 LSB = 0.5  Analog voltage $V_a$ Comparator  Programmer  Offiset voltage = 1/2 LSB = 0.5  Analog voltage $V_a$ Programmer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Diagr<br>2M    |

|       | The successive approximation A/D converter is as shown in fig. An analog voltage (Va) is constantly compared with voltage Vi, using a comparator. The output produced by comparator (Vo) is applied to an electronic Programmer. If Va=Vi, then Vo=0 & then no conversion is required. The programmer displays the value of Vi in the form of digital O/P.  But if Va Vi, then the O/P is changed by the programmer.  If Va> Vi, then value of Vi is increased by 50% of earlier value.  But if Va< Vi, then value of Vi is decreased by 50% of earlier value.  This new value is converted into analog form, by D/A converter so as to compare it with Va again. This procedure is repeated till we get Va=Vi. As the value of Vi is changed successively, this method is called as successive-approximation A/D converter. | Expla<br>ion 2 |

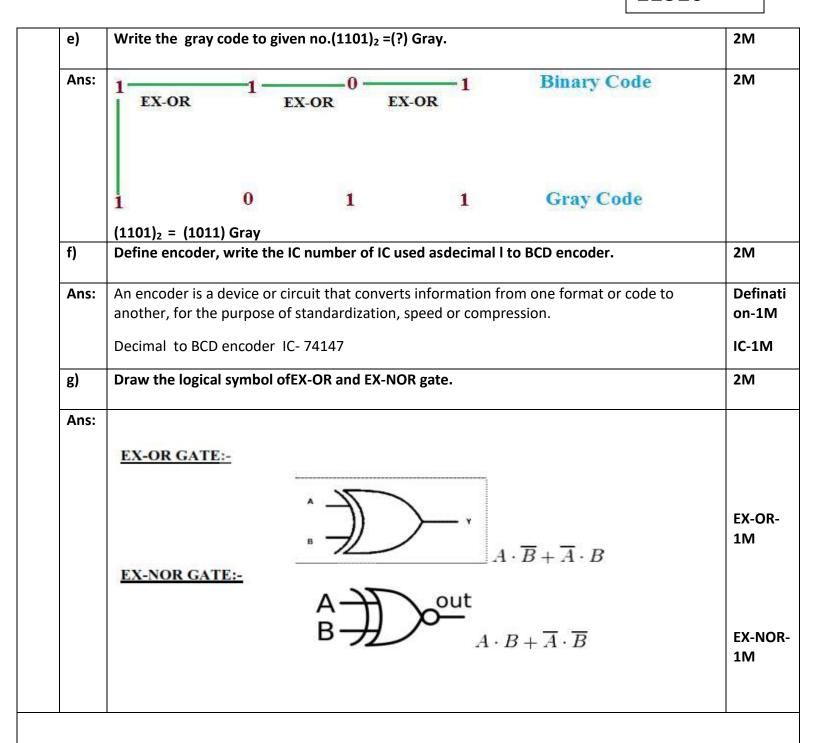

| b)    | Describe the operation of R-S flip flop using NAND gates only .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4M             |

| Ans:  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

| Allo. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

# SUMMER-19 EXAMINATION Model Answer

Subject Code:

22320

Logical Diagram 2M

### **Description/explanation-**

When clock = 0, the outputs of NAND gates 3 and 4 will be forced to be 1 irrespective of the values of S and R. That means R'= S' = 1. Hence the outputs of basic SR/F/F i.e. Q n+1 and  $\overline{Qn+1}$  will not change. Thus if clock = 0, then there is no change in the output of the clocked SR flip-flop.

### Case I: S = R = 0, clock = 1: No change

If S=R=0 then outputs of NAND gate 3 and 4 are forced to become 1.

Hence R' and S' both will be equal to 1. Since R' and S' are the inputs of the basic S - R flipflop using NAND gates. There will be no change in the state of outputs.

### Case II : S = 1, R = 0, clock = 1: Set

Now S=0, R=1 and a positive going edge is applied to the clock  $\,$

Output of NAND 3 i.e. R' = 0 and output of NAND 4 i.e. S' = 1.

Hence output of SR flip-flop is Q n+1 = 1 and  $\overline{Qn+1}$  = 0.

This is the set condition.

#### Case III : S = 0, R = 1, clock = 1: Reset

Now S=0, R=1 and a positive edge is applied to the clock input.

Since S=0, output of NAND – 3 i.e. R'= 1. And as R' = 1 and clock = 1 the output of NAND-4 i.e. S' = 0. Hence output of SR flip-flop is Q n+1 = 0 and  $\overline{Qn+1}$  = 1.

This is the reset condition.

### Case IV: S = 1, R = 1, clock = 1: Undefined/forbidden

As S=1, R=1 and clock = 1, the outputs of NAND gates 3 and 4 both are 0 i.e. S' = R'=0. So both the outputs Q n+1 = 1 and  $\overline{Qn+1}$  Hence output is Undefined/ forbidden.

Explanat ion 2M

Explanat ion without clock pulse must also be consider ed

# SUMMER-19 EXAMINATION

Model Answer \_\_Subject Code:

tt Code: | 22320

|    | CLK               |                | INPUTS         | OU              | TPUTS             | REMARK    |                                                                         |

|----|-------------------|----------------|----------------|-----------------|-------------------|-----------|-------------------------------------------------------------------------|

|    |                   | S              | R              | Qn+1            | Qn+1              |           |                                                                         |

|    | 0                 | x              | Х              | Qn              | $\overline{Qn}$   | No change |                                                                         |

|    | 1                 | 0              | 0              | Qn              | $\overline{Qn}$   | No change |                                                                         |

|    | 1                 | 0              | 1              | 0               | 1                 | Reset     |                                                                         |

|    | 1                 | 1              | 0              | 1               | 0                 | Set       |                                                                         |

|    | 1                 | 1              | 1              | ?               | ?                 | Forbidden |                                                                         |

| c) | Give classif      | fication of me | mory and compa | are RAM and RON | /I (any four poin | ts)       | 4M                                                                      |

|    | PRIMA ROM -PR -EP |                | MEI            | MORY AM DRAI    | 11.08             | D<br>D    | ation<br>2M<br>Considered is<br>even in Secondary<br>memoris not writte |

|    | Compariso         | n between R    | AM and ROM AM  |                 | RAM               |           |                                                                         |

|    | 1. Te             | mporary Stora  |                | 1.Permane       |                   |           |                                                                         |

|    | 2 .Sto            | ore data in MB | Ss.            | 2.Store dat     | a in GBs.         |           |                                                                         |

|    | l <u> </u>        | olatile .      |                | 3.Non-Vola      |                   |           |                                                                         |

# SUMMER-19 EXAMINATION Model Answer

Subject Code:

|      | 4. Writing data is Faster.                                                            | 4. Writing data is Slower.                                                                                 |               |

|------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------|

|      |                                                                                       |                                                                                                            | Comp<br>son 2 |

| d)   | State the applications of shift register                                              | r.                                                                                                         | 4M            |

| Ans: | _                                                                                     | serial converter, which converts the parallel dat tter section after Analog to Digital Converter (Al       |               |

|      | -                                                                                     | rallel converter, which converts the serial data i<br>ver section before Digital to Analog Converter (D    |               |

|      | 3] Shift register along with some additiones. Hence, it is used as <b>sequence</b> ge | tional gate(s) generate the sequence of zeros arenerator.                                                  |               |

|      | _                                                                                     | <b>nters</b> . There are two types of counters based on flop is connected to the serial input. Those are R |               |

| Q.<br>No. | Sub<br>Q. N. | Answers                                                                                                                                            | Marking<br>Scheme  |

|-----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 4         |              | Attempt any THREE of the following :                                                                                                               | 12- Total<br>Marks |

|           | (a)          | Subtract the given number using 2's compliment method: $ (i) \qquad (11011)_2 - (11100)_2 \\ (ii) \qquad (1010)_2 \ - \ (101)_2 $                  | 4M                 |

|           | Ans:         | i) Subtract (11011) <sub>2</sub> – (11100) <sub>2</sub> using 2's complement binary arithmetic.  Solution:                                         |                    |

|           |              | $(11011)_2 - (11100)_2$<br>Now,<br>2's complement of $(11100)_2$ = 1's complement of $(11100)_2$ +1<br>1's complement of $(11100)_2$ = $(00011)_2$ | 2's<br>comple      |

# SUMMER-19 EXAMINATION Model Answer

\_Subject Code:

|     | 2's complement = 0              | 00011+1                | = 0010  | 00                 |       |       |                     |                                      | 1M                  |

|-----|---------------------------------|------------------------|---------|--------------------|-------|-------|---------------------|--------------------------------------|---------------------|

|     | Therefore,                      |                        | 1       | 1                  | 0     | 1     | 1                   |                                      |                     |

|     | +                               |                        | 0       | 0                  | 1     | 0     | 0                   |                                      |                     |

|     |                                 |                        | 1       | 1                  | 1     | 1     | 1                   |                                      |                     |

|     | There is no carry it            | indicates              | that    | resul              | ts is | nega  | itive and           | nd in 2's complement form i.e.(11111 | )2.                 |

|     | Therefore, for getti            | ng true v              | alue i  | .e.(+1             | L) ta | ke 2  | 's comp             | plement of (11111) is                |                     |

|     | 1's complement + 1              | _                      |         |                    |       |       |                     |                                      | Fina                |

|     | = 00000 + 1                     |                        |         |                    |       |       |                     |                                      | Ansv                |

|     | Ans= (00001) <sub>2</sub>       |                        |         |                    |       |       |                     |                                      | 1M                  |

|     | Ans: (11011) <sub>2</sub> – (11 | 100)2 = 2              | 's con  | nplen              | nent  | of (2 | 11111) <sub>2</sub> | $_{2} = (-1)_{10}$                   |                     |

|     | ii) Subtract                    | t (1010) <sub>2</sub>  | - (10   | 1) <sub>2</sub> us | sing  | 2's c | omplen              | ment binary arithmetic.              |                     |

|     | 2's complement of               | (0101) <sub>2</sub> =  | : 1's c | ompl               | eme   | nt o  | f ( <b>0101)</b>    | ) <sub>2</sub> +1                    |                     |

|     | 1's complement of               | (0101)2                | = (101  | .0)2               |       |       |                     |                                      |                     |

|     | 2's complement = 1              | .010+1 =               | 1011    |                    |       |       |                     |                                      | 2's                 |

|     | Therefore,                      | 1                      | . 0     | 1                  | 0     |       |                     |                                      | com                 |

|     |                                 | +                      |         |                    | 4     |       |                     |                                      | men                 |

|     |                                 | 1                      | . 0     | 1                  | 1     |       |                     |                                      |                     |

|     |                                 | 1                      |         |                    |       |       |                     |                                      |                     |

|     |                                 | 1 0                    | 1       | 0                  | 1     |       |                     |                                      |                     |

|     |                                 |                        |         |                    |       |       |                     |                                      |                     |

|     | There is carry ignor            | e it, whic             | h indi  | cates              | s tha | t res | ults is p           | positive i.e.(+5)                    |                     |

|     | = (0101) <sub>2</sub>           |                        |         |                    |       |       |                     |                                      |                     |

|     | Ans: (1010) <sub>2</sub> - (101 | L) <sub>2</sub> = (010 | 1)2= (  | +5) <sub>10</sub>  |       |       |                     |                                      | Final<br>Answ<br>1M |

| (b) | Stare De-Morgan's               | thooren                | n and   | nrov               | o 20  | v on  | Δ                   |                                      | 4M                  |

**SUMMER-19 EXAMINATION Subject Name: Digital technique**

Subject Code:

22320

Ans:

**Model Answer**

De Morgan's 1<sup>st</sup> Theorem: It states that the compliment of sum is equal to the product of the compliment of individual variables.

Stateme nts-1M each

$$(\overline{A+B}) = \overline{A} \ \overline{B}$$

Anyone proof -2M

Proof:

| A | В | $\overline{A}$ | $\overline{B}$ | A+B | $(\overline{A+B})$ | $\overline{A}$ $\overline{B}$ |

|---|---|----------------|----------------|-----|--------------------|-------------------------------|

| 0 | 0 | 1              | 1              | 0   | 1                  | 1                             |

| 0 | 1 | 1              | 0              | 1   | 0                  | 0                             |

| 1 | 0 | 0              | 1              | 1   | 0                  | 0                             |

| 1 | 1 | 0              | 0              | 1   | 0                  | 0                             |

# De Morgan's 2<sup>nd</sup> Theorem:

It states that the compliment of product is equal to the sum of the compliments of individual variables.

$$(\overline{A}\overline{B}) = \overline{A} + \overline{B}$$

Proof:

| А | В | $\overline{A}$ | $\overline{B}$ | A.B | $(\overline{AB})$ | $\overline{A} + \overline{B}$ |

|---|---|----------------|----------------|-----|-------------------|-------------------------------|

| 0 | 0 | 1              | 1              | 0   | 1                 | 1                             |

| 0 | 1 | 1              | 0              | 0   | 1                 | 1                             |

| 1 | 0 | 0              | 1              | 0   | 1                 | 1                             |

| 1 | 1 | 0              | 0              | 1   | 0                 | 0                             |

(c)

Compare between PLA and PAL.

4M

# SUMMER-19 EXAMINATION Model Answer

Subject Code:

| Ans: | PLA PAL                                                                                                         | Any four              |

|------|-----------------------------------------------------------------------------------------------------------------|-----------------------|

|      | 1) Both AND and OR arrays are programmable 1) OR array is fixed and AND array is programmable.                  | 4 points-<br>1M each  |

|      | Costliest and complex than PAL     Cheaper and simpler                                                          |                       |

|      | 3) AND array can be programmed to get desired minterms.  3) AND array can be programmed to get desired minterm. |                       |

|      | 4) Large number of functions can be implemented.  4) Provides the limited number of functions.                  |                       |

|      | 5) Provides more programming 5) Offers less flexibility, but more likely used.                                  |                       |

| (d)  | Reduce the following expression using K-map and implement it $F(A,B,C,D) = \Pi M (1,3,5,7,8,10,14)$             | 4M                    |

| Ans: | AB 00 01 11 10                                                                                                  | Kmap-                 |

|      | $(A+\overline{D})$                                                                                              | Pairs-<br>1.5M        |

|      | 0 0 1 3 2                                                                                                       | Final<br>Ans-<br>1.5M |

|      | 0 1 4 0 5 7 6                                                                                                   | 1.5141                |

|      | 1 1 12 13 15 $\sqrt{0}$ 14 $\overline{(A+C+D)}$                                                                 |                       |

|      | 10 8 9 11 0 10                                                                                                  |                       |

|      | (A+B+D)                                                                                                         |                       |

|      | $F(A,B,C,D)=(A+\overline{D}) (\overline{A}+\overline{C}+D) (\overline{A}+B+D)$                                  |                       |

# SUMMER-19 EXAMINATION Model Answer

Subject Code:

# SUMMER-19 EXAMINATION Model Answer

Subject Code:

22320

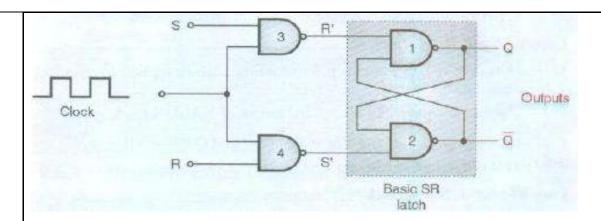

If CLK= 1 and J=K=O then the output Q and  $\bar{Q}$  will not change their state.

If J=0 and K= 1 then JK flip flop will reset and Q= 0 &  $\bar{Q}$  =1

If J=1 and K=0 then output will be set and Q=1 &  $\bar{Q}$  =0

If J= K=1 then Q &  $\bar{Q}$  outputs are inverted and FF will toggle

### **Race Around condition:**

Race around condition occurs in J K Flip-flop only when J=K=1 and clock/enable is high (logic 1) as shown below-

In JK Flip-flop when J=K=1 and when clock goes high, output should toggle (change to opposite state), but due to multiple feedback, output changes/toggles many times till the clock/enable is high.

Thus toggling takes place more than once, called as racing or race around condition.

| Q.<br>No. | Sub<br>Q. N. | Answers                                                                 | Marking<br>Scheme  |

|-----------|--------------|-------------------------------------------------------------------------|--------------------|

| 5.        |              | Attempt any TWO of the following:                                       | 12- Total<br>Marks |

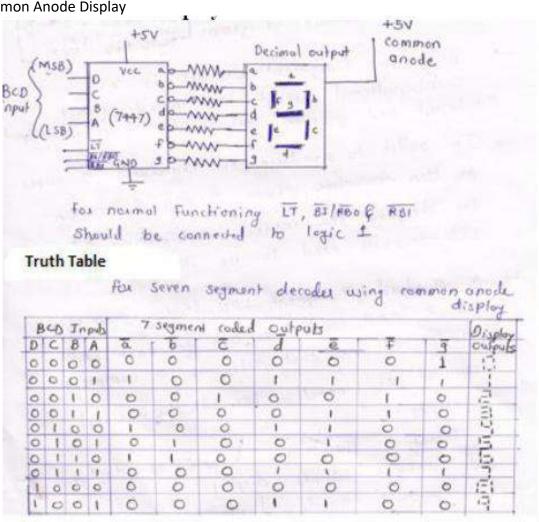

|           | a)           | Design BCD to seven segment decoder using IC 7447 with its truth table. | 6M                 |

Ans:

**SUMMER-19 EXAMINATION Model Answer**

**Subject Code:**

22320

Note: Any one type of display shall be considered

1. BCD to 7 segment decoder is a combinational circuit that accepts 4 bit BCD input and generates appropriate 7 segment output.

- 2. In order to produce the required numbers from 0 to 9 on the display the correct combination of LED segments need to be illuminated.

- 3. A standard 7 segment LED display generally has 8 input connections, one from each LED segment & one that acts as a common terminal or connection for all the internal segments

- 4. Therefore there are 2 types of display 1. Common Anode Display 2. Common Cathode Display:

Circuit Diagram 2M

**Explaina**

tion 2M

Common Anode Display

Truth **Table** 2M

# SUMMER-19 EXAMINATION Model Answer

Subject Code:

# SUMMER-19 EXAMINATION Model Answer

**Subject Code:**

22320

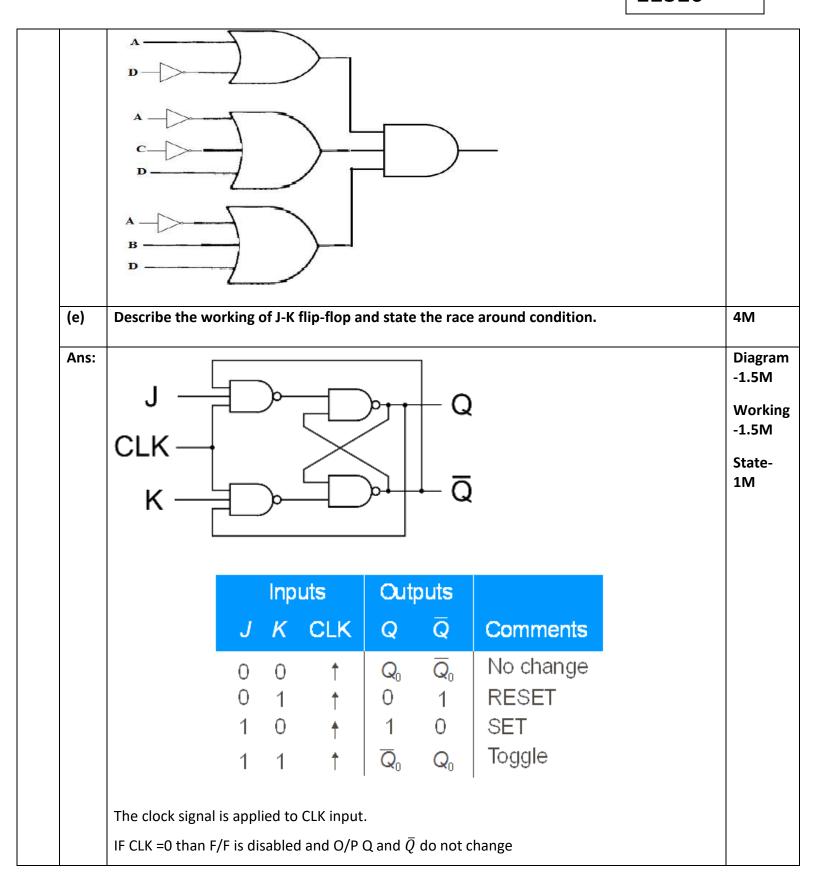

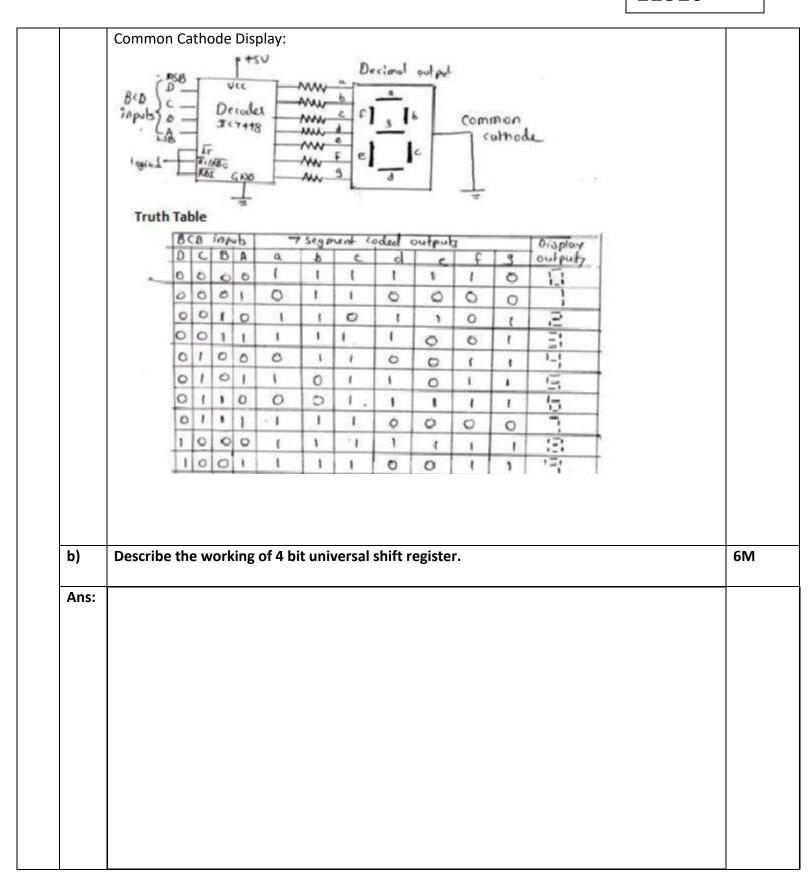

Circuit Diagram 3M

Working 3M

Fig:4 bit universal shift register

### Working:

- 1. **PARALLEL LOAD**: When mode control (M) is connected to logic 1, AND gates 2, 4, 6, 8 will be enables and AND gates 1, 3,5,7, will be disabled . The 4-bit binary data will be loaded parallel. The clock-2 input will be applied to the flip-flops , since M=1, AND gates -10 is enabled and gate-9 is disabled. Input will transfer parallel data to QA to QD outputs.

- 2. **SHIFT RIGHT**: When mode control (M) is connected to logic 0, AND gates 1,3,5,7 will be enabled and gates 2, 4,,6, 8,will be disabled. The data will be shifted serially. The clock -1, input will be applied to the flip-flops, Since M = 0, AND gates 9 is enabled, and gates -10 is disabled. The data is shifted serially to right from QA to QD.

- 3. **SHIFT LEFT:** When mode control (M) is connected to logic 1, AND gates 2,4,6,8 will be enabled. This mode permits parallel loading of the resister and shift -left operation. The shift -left operation can be accomplished by connecting the output of each flip flop to the parallel input of the previous flip- flop and serial input is applied at the input.

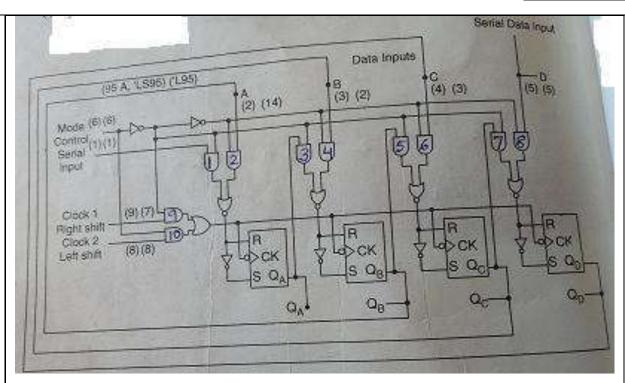

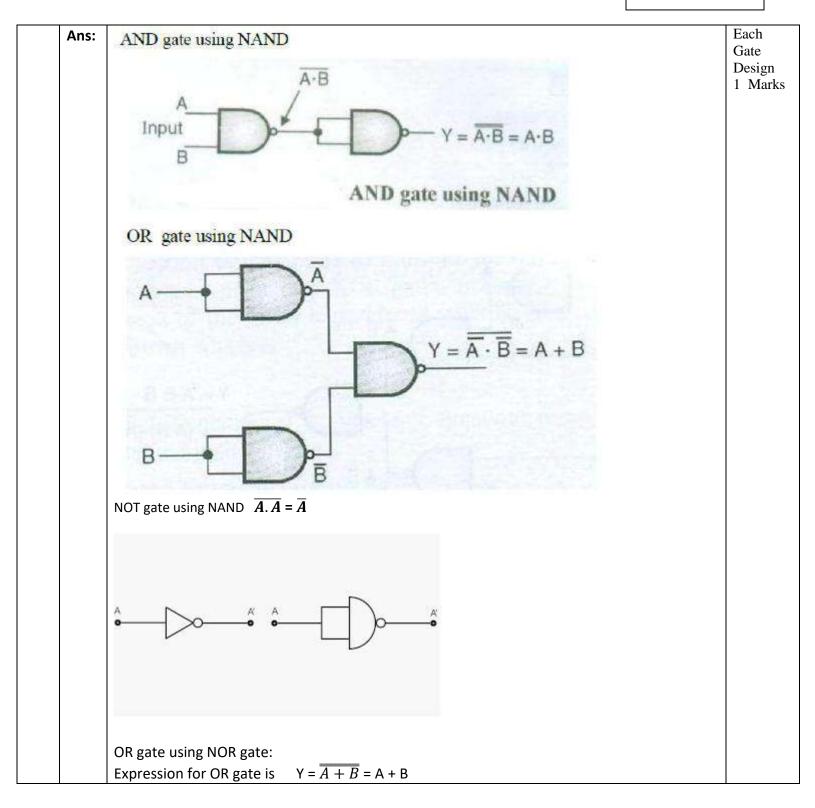

- c) Design basic logic gates using NAND and NOR gate.

6M

# SUMMER-19 EXAMINATION Model Answer

Subject Code:

# SUMMER-19 EXAMINATION Model Answer

Model Answer \_\_Subject Code:

22320

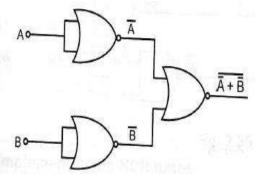

AND gate using NOR gate:

Expression for AND gate is Y =  $\overline{A} + \overline{B} = \overline{A}.\overline{B} = A.B$  (Applying De Morgan"s theorem)

NOT gate using NOR Y=  $\overline{A+A}$  =  $\overline{A}$

| Q.<br>No. | Sub<br>Q. N. | Answers                                                                                                                                                                                                             | Marking<br>Scheme    |

|-----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 6.        |              | Attempt any TWO of the following:                                                                                                                                                                                   | 12- Total<br>Marks   |

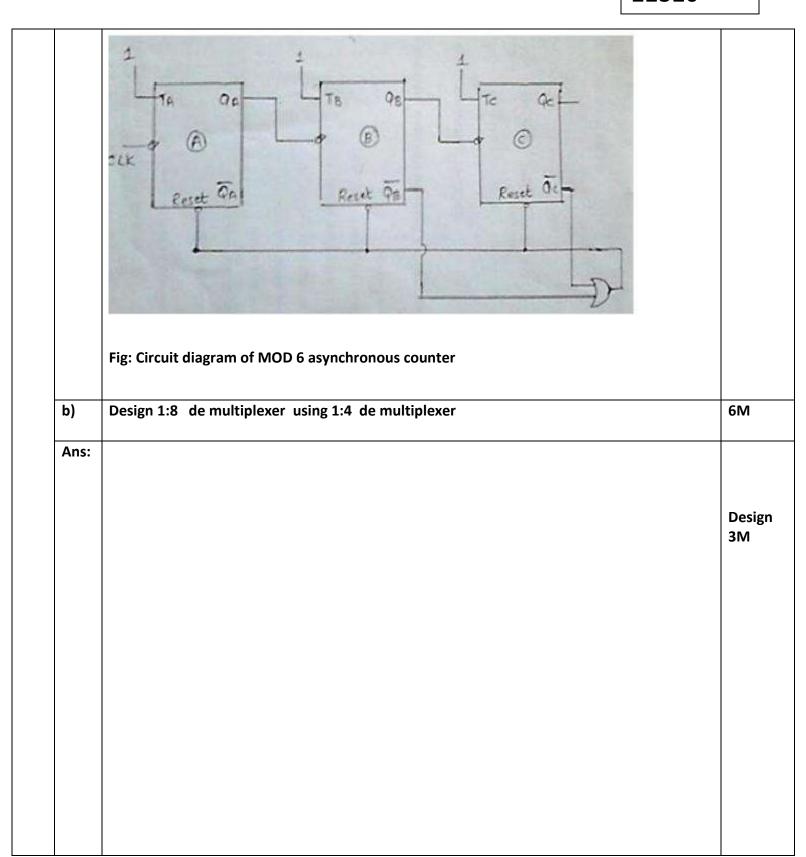

|           | a)           | Design a mod-6 Asynchronous counter with truth-table and logic.                                                                                                                                                     | 6M                   |

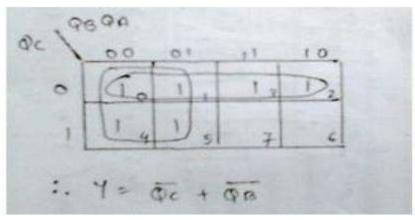

|           | Ans:         | MOD 6 asynchronous counter will require 3 flip flops and will count from 000 to 101. Rest of the states are invalid. To design the combinational circuit of valid states, following truth table and K-map is drawn: |                      |

|           |              |                                                                                                                                                                                                                     | Truth<br>Table<br>2M |

### SUMMER-19 EXAMINATION Model Answer

Subject Code:

22320

| Qc | Q <sub>B</sub> | Q <sub>A</sub> | Reset Logic |

|----|----------------|----------------|-------------|

| 0  | 0              | 0              | 1           |

| 0  | 0              | 1              | 1           |

| 0  | 1              | 0              | 1           |

| 0  | 1              | 1              | 1           |

| 1  | 0              | 0              | 1           |

| 1  | 0              | 1              | 1           |

| 1  | 1              | 0              | 0           |

| 1  | 1              | 1              | 0           |

From the above truth table, we draw the K-maps and get the expression for the MOD 6 asynchronous counter.

Logic Diagram 2M

Fig: K-map for above truth table

Thus reset logic is OR of complemented forms of QC and QB. This will be given to the reset inputs of the counter so that as soon as count 110 reaches, the counter will reset. Thus the counter will count from 000 to 101. The implementation of the designed MOD 6 asynchronous counter is shown below:

Circuit Diagram 2M

# SUMMER-19 EXAMINATION Model Answer

**Subject Code:**

# SUMMER-19 EXAMINATION Model Answer

Subject Code:

22320

Truth

Table

3M

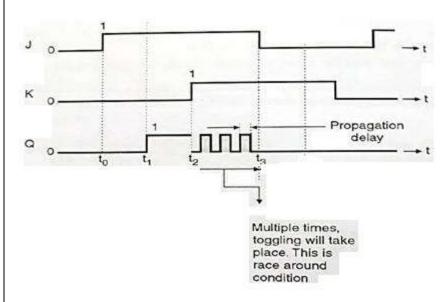

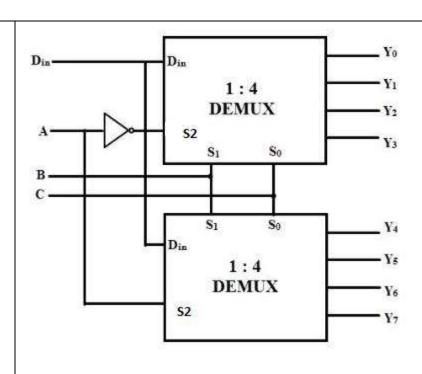

Fig:1:8 Demultiplexer using 1:4 demultiplexer

| Data Input | Select Inputs  |    |    | Outputs |                |    |                |    |                |    |    |  |

|------------|----------------|----|----|---------|----------------|----|----------------|----|----------------|----|----|--|

| D          | S <sub>2</sub> | Sı | 50 | Υ,      | Y <sub>6</sub> | Y, | Υ <sub>4</sub> | Υ3 | Y <sub>2</sub> | Yı | Yo |  |

| D          | 0              | 0  | 0  | 0       | 0              | 0  | 0              | 0  | 0              | 0  | D  |  |

| D          | 0              | 0  | 1  | 0       | 0              | 0  | 0              | 0  | 0              | D  | 0  |  |

| D          | 0              | 1  | 0  | 0       | 0              | 0  | 0              | 0  | D              | 0  | 0  |  |

| D          | 0              | 1  | 1  | 0       | 0              | 0  | 0              | D  | 0              | 0  | 0  |  |

| D          | 1              | 0  | 0  | 0       | 0              | 0  | D              | 0  | 0              | 0  | 0  |  |

| D          | 1              | 0  | 1  | 0       | 0              | D  | 0              | 0  | 0              | 0  | 0  |  |

| D          | 1              | 1  | 0  | 0       | D              | 0  | 0              | 0  | 0              | 0  | 0  |  |

| D          | 1              | 1  | 1  | D       | 0              | 0  | 0              | 0  | 0              | 0  | 0  |  |

Fig: Truth Table of 1:8 Demultiplexer.

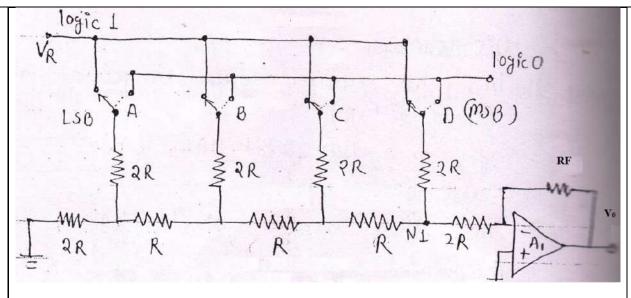

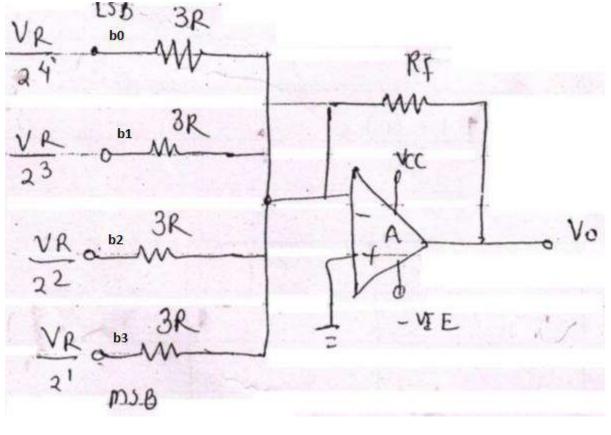

| c)   | Draw the circuit diagram of 4 bit R-2R ladder DAC and obtain its output voltage expression | 6M |

|------|--------------------------------------------------------------------------------------------|----|

| Ans: |                                                                                            |    |

# SUMMER-19 EXAMINATION Model Answer

Subject Code:

22320

2M

2M

Fig 1: 4 bit R-2R ladder DAC

Fig 2:Simplified circuit diagram of Fig 1

Therefore output analog voltage Vo is given by,

**SUMMER-19 EXAMINATION**

**Model Answer**

\_Subject Code:

$$V_{0} = -\left(\frac{Pf}{3R} \cdot \frac{VR}{2^{4}} b_{0} + \frac{Pf}{3R} \cdot \frac{VR}{2^{3}} b_{1} + \frac{Pf}{3R} \cdot \frac{VR}{2^{4}} b_{2} + \frac{Pf}{3R} \cdot \frac{VR}{2^{1}} b_{3}\right)$$

$$V_{0} = -\left(\frac{Pf}{3R}\right) \left(\frac{VR}{2^{4}}\right) \left[8b_{3} + 4b_{2} + 2b_{1} + b_{0}\right]$$

$$V_{0} = -\left(\frac{Pf}{3R}\right) \left(\frac{VR}{2^{4}}\right) \left[8b_{3} + 4b_{2} + 2b_{1} + b_{0}\right]$$